NP1003墳梡椺嘇 傊偉乣偟偭偔 (HASIC)

2004擭1寧9擔 敪昞

2004擭1寧11擔

僉儍僾僠儍偟偨僒儞僾儖壒惡傪宖嵹

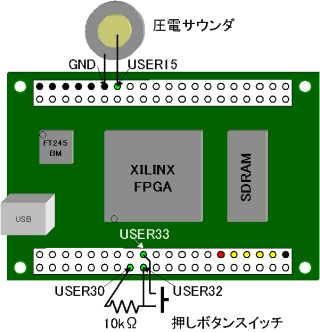

HuMANDATA幮惢XSP006-200偵懳墳

FFT僗儁僋僩儔儉應掕

傊偉乣偟偭偔偲偼

丂乽傊偉乣偟偭偔乿偼FPGA儚儞僠僢僾偱峔惉偡傞傊偉儃僞儞偱偡丅

丂USB偵偮側偄偩弖娫丄偁傞偄偼僾僢僔儏儃僞儞傪墴偟偨傝丄USB偐傜僨乕僞傪憲傞偨傃偵埑揹僒僂儞僟偐傜乽傊偉乣乿偲扙椡姶偺偁傞壒偑柭傝傑偡丅

丂乽傊偉乣偟偭偔乿偺壒傪暦偔丂(he-captured.wav

205kB)

仸埑揹慺巕偱偼側偔丄PC偺儔僀儞擖椡偐傜庢傝崬傫偩壒惡偱偡丅

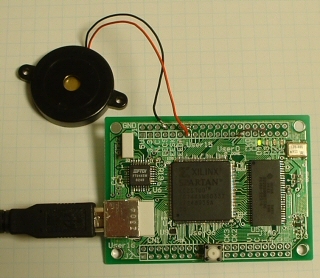

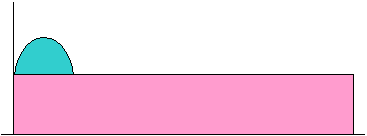

幨恀1

傊偉乣偟偭偔偺奜娤

丂側偍丄乽傊偉乣偟偭偔乿偺岅尮偱偡偑丄FPGA偼峀媊偺ASIC偲偄偊傑偡偺偱丄乽傊偉乣乿偲ASIC傪偐偗偰丄HASIC偲柤偯偗偰偄傑偡丅

婡擻奣梫

丂FPGA撪偺僽儘僢僋RAM傪攇宍ROM偲偟偰巊梡偟丄FPGA撪偵Delta-Sigma宆1價僢僩DAC傪峔惉偟偰丄FPGA偺I/O偐傜捈愙傾僫儘僌怣崋傪弌椡偟傑偡丅

丂傊偉儃僞儞偼丄懡悢楢懕偱墴偟偨偲偒偵丄乽傊傊傊偉乣乿偲側傜偢偵丄

|

傊偉乣乣 |

丂偲丄廳側傝崌偭偰暦偙偊傑偡丅乽傊偉乣偟偭偔乿偱偼偙偺廳側傝崌偄婡擻傪4懡廳傑偱幚憰偟偰偄傑偡丅

丂側偍丄墴偟儃僞儞偵偼丄50ms偺晄姶帪娫傪愝偗偰僠儍僞儕儞僌傪彍嫀偟偰偄傑偡丅

幚懱攝慄恾

丂埲壓偵丄乽傊偉乣偟偭偔乿偺嶌傝曽傪帵偟傑偡丅

丂偙傟偩偗偱丄埑揹僒僂儞僟偑乽傊偉乣乿偲尵偄傑偡丅

揹尮搳擖偱乽傊偉乣乿偑側傞偲偄偆偙偲 -僐儞僼傿僌ROM-

丂NP1003偼僐儞僼傿僌ROM偑僆儞儃乕僪偱昗弨搵嵹偝傟偰偄傞偨傔丄USB働乕僽儖傪憓擖偲摨帪偵乽傊偉乣乿傪敪惡偱偒丄偡偖偵妝偟傔傑偡丅

丂傕偟丄婎斅忋偵僐儞僼傿僌ROM偑側偔丄偄偪偄偪PC偐傜僟僂儞儘乕僪偟側偗傟偽乽傊偉乣乿偑柭傜側偄傛偆偱偼柺敀偝偑敿尭偟偰偟傑偆偱偟傚偆丅

Delta Sigma 1價僢僩DAC偺偟偔傒

丂娙扨偵怽偟傑偡偲丄1偲0傪崅懍偵愗傝懼偊偰丄偦偺枾搙偱拞娫抣傪弌偡偲偄偆傕偺偱偡丅

丂娙扨側僀儊乕僕恾偱丄PWM偲斾妑偟偰傒傑偟傚偆丅

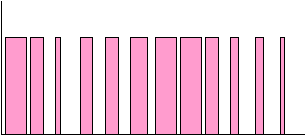

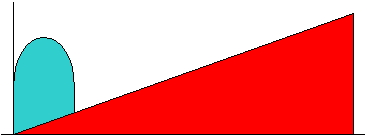

恾2 PWM弌椡偺攇宍

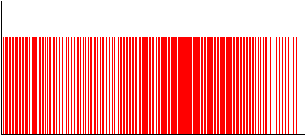

恾3 Delta Sigma 1價僢僩 DAC弌椡偺攇宍

丂PWM傕Delta Sigma傕侾偲0偺枾搙偱拞娫抣傪昞尰偡傞曽朄側偺偱偡偑丄Delta Sigma偺曽偑偒傔嵶偐偄弌椡偑壜擻偱偡丅攇宍偼偳偪傜傕僊僓僊僓偟偰偄傑偡偑丄廃攇悢惉暘偱尒傞偲丄師偺傛偆偵戝偒側嵎偑偁傝傑偡丅

恾4 PWM弌椡偺僗儁僋僩儔儉

恾5 Delta Sigma 1價僢僩 DAC弌椡偺僗儁僋僩儔儉

丂PWM偼掅偄廃攇悢惉暘偵崅偄廃攇悢惉暘偵傕偩偄偨偄堦條側僲僀僘傪帩偪傑偡偑丄Delta Sigma偱偼偦偺僲僀僘偑崅偄曽傊偲墴偟傗傜傟偰偟傑偄丄掅偄廃攇悢惉暘偼鉟楉側僗儁僋僩儖偵側傝傑偡丅幚嵺丄帹偵暦偙偊傞偺偼20kHz偔傜偄傑偱側偺偱丄悢昐乣悢MHz偵偁傞僲僀僘偼帹偵暦偙偊偢丄僋儕乕儞側壒偑暦偙偊傞偺偱偡丅

丂側偍丄杮棃偼DAC偺弌椡偵儘乕僷僗僼傿儖僞傪偮側偘傞傋偒偱偡丅

丂儘乕僷僗僼傿儖僞傪偄傟側偄偲丄崅廃攇惉暘偑偦偺傑傑弌椡偝傟偰偟傑偄傑偡丅偟偨偑偭偰丄埑揹慺巕偼偍偦傜偔挻壒攇傪嶵偒嶶傜偟偰偄傑偡丅傕偪傠傫帹偵偼暦偙偊傑偣傫丅傑偨丄攝慄偑挿偔側傞偲丄攝慄偑傾儞僥僫偲側偭偰揹帴揑僲僀僘傪廃埻偵嶵偒嶶傜偟傑偡丅僷儚乕MOS

FET側傫偐傪偮側偄偱丄僶僠僶僠ON/OFF偟偨傜丄崅廃攇揹棳偱晧壸偑擱偊傞偐傕偟傟傑偣傫丅

丂偙偺偨傔丄Delta Sigma DAC偺弌椡偵偼儘乕僷僗僼傿儖僞傪擖傟傞偙偲傪嫮偔偍偡偡傔偟傑偡丅偟偐偟丄CR宆偺僼傿儖僞偼僄僱儖僊傪徚旓偟傑偡偺偱丄僄僱儖僊偑栜懱柍偄偩偗偱側偔丄僷儚乕MOS FET偺戝偒側傾儞僾偱偼敪擬偟偦偆偱偡偹丅偙偺偨傔丄嵟廔抜奒偱LC宆偺僼傿儖僞傪巊偆偺偑堦斒揑偩偦偆偱偡丅僐僀儖偲僐儞僨儞僒偱偼僄僱儖僊傪徚旓偟傑偣傫偺偱丅

丂Delta Sigma DAC偺幚憰偵偮偄偰偼丄XILINX偺傾僾儕働乕僔儑儞僲乕僩 XAPP155偑偲偰傕娙扨側曽朄傪徯夘偟偰偄傑偡丅

丂側偍丄Sigma Delta 1價僢僩ADC偲偄偺傕偁傝傑偡丅偙傟傪巊偊偽丄FPGA扨懱偱ADC偲DAC偑峔惉偱偒傑偡丅懍搙偼偁傑傝懍偔偼側偄偺偱偡偑丄悢10k

sample/sec丄10價僢僩偔傜偄偺DAC傗ADC偼娙扨偵偮偔傟偰偟傑偄傑偡丅

丂偦傟偼偦傟偱丄傑偨暿偺婡夛偵丅

攇宍偺應掕

丂Sigma Delta DAC偱偼丄偦偺攇宍傪尒偰傕偲偰傕傾僫儘僌偵偼尒偊傑偣傫丅

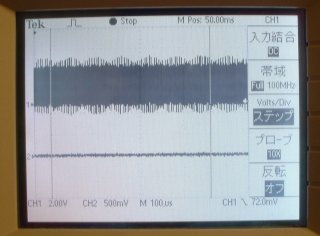

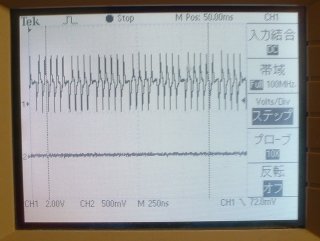

幨恀3 Delta Sigma 1價僢僩 DAC弌椡偺攇宍

丂傛傝奼戝偟偰偄偔偲偙偺傛偆偵枾搙偺嵎偑尒偊偰偒傑偡丅

幨恀4 Delta Sigma 1價僢僩 DAC弌椡偺攇宍攇宍

丂埑揹僒僂儞僟傪偮側偖偲丄FPGA偺I/O僺儞偑側偤偐僴僀僷僗僼傿儖僞偺傛偆側攇宍偵側傝傑偟偨丅埑揹慺巕偵抁帪娫偺娫偵僄僱儖僊偑拁愊偝傟偨傝奐曻偝傟偨傝傪孞傝曉偡偺偱偟傚偆偐丠

丂FPGA偺偨傔偵傕丄廃埻偺娐嫬偺偨傔偵傕偁傑傝椙偄偲偼偄偊側偄偺偐傕偟傟傑偣傫丅

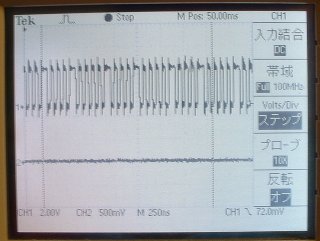

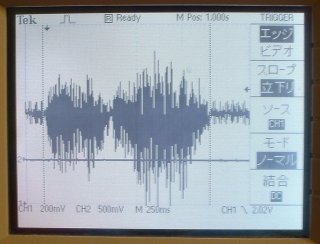

幨恀5 埑揹僒僂儞僟忋偺揹埑

丂LPF傪偮側偖偲丄偙偺傛偆偵傾僫儘僌怣崋偑庢傝弌偣傑偡丅側偍丄幨恀6偼乽傊偉乣乿傪丄乽傊偉乣 傊傊傊偉乣乿偺梫椞偱4夞柭傜偟偰偄傑偡丅

幨恀6 LPF傪捠偟偨応崌偺揹埑攇宍

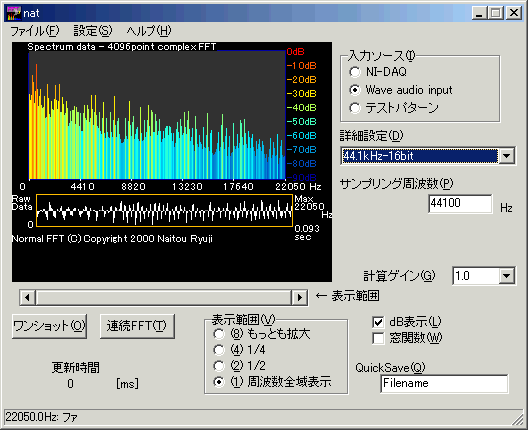

丂乽傊偉乣乿偺壒傪PC偺儅僀僋擖椡偐傜擖椡偟丄應掕偟偨僗儁僋僩儔儉偱偡丅

崱屻偺曽恓

丂堦斒偵丄乽傊偉乣乿偺壒惡偼丄10kHz偔傜偄傑偱偺惉暘傪娷傫偱偄傞偺偱丄僒儞僾儕儞僌廃攇悢偑掅偄偲撥偭偨壒偵側偭偰偟傑偄傑偡丅偟偐偟丄僒儞僾儕儞僌廃攇悢傪忋偘傞偲丄FPGA撪偺(僽儘僢僋RAM偱偮偔傞)ROM偺梕検偑懌傝側偔側傝傑偡丅偦偙偱丄壒惡傪埑弅偟偰ROM偵婰壇偟丄偦傟傪儕傾儖僞僀儉偵揥奐偟偰敪惡偡傞偺偑儀僗僩偐偲巚偄傑偡丅壒惡埑弅偵偼丄ADPCM傗CELP側偳偄傠偄傠偁傝丄傑偨丄儊乕僇乕宯偺ADPCM偺傾儖僑儕僘儉偼偄傠偄傠偲儔僀僙儞僗偑偁傞偲巚偆偺偱丄G.726偺傾儖僑儕僘儉傪扵偟偰偄傞偺偱偡偑丄僱僢僩偱娙扨偵偼棊偪偰偄傑偣傫丅G.726傪巊偭偰壒惡傪埑弅偟丄僒儞僾儕儞僌儗乕僩傪彮側偔偲傕20kHz偔傜偄傑偱偼忋偘傜傟傟偽丄壒幙偑偲偰傕傛偔側傞偲巚偄傑偡丅

丂偁偲丄NP1003偩偗偱側偔丄僸儏乕儅儞僨乕僞偝傫偺XSP006偱傕摦偔偲巚偄傑偡丅墴偟儃僞儞偲埑揹僒僂儞僟偑偁傞偺偱丄乽傊偉乣偟偭偔乿偑偡偖偵峔惉偱偒偦偆偱偡丅偟偐傕丄7僙僌偺LED偑偁傞偺偱丄僇僂儞僞偵傕側傝偦偆偱偡丅

仺偱偒傑偟偨丅

XC2S200側傜偽丄傕偆彮偟挿偄壒惡傕擖傝偦偆偱偡丅

丂崱夞偺婰帠偼丄Sigma Delta偺棟榑揑側晹暘偵偼怺擖傝偣偢偵偝傜偭偲彂偒傑偟偨丅巹傕Sigma Delta傪曌嫮偟偰丄偦偺偆偪崅搙側夝愢偑偱偒傞傛偆偵偟傑偡丅

僜乕僗僐乕僪

NP1003梡

- VHDL僜乕僗 main.vhd 丒丒丒儊僀儞偺僜乕僗僐乕僪

- VHDL僜乕僗 dac.vhd 丒丒丒1價僢僩 SigmaDelta DAC偺僜乕僗僐乕僪

- VHDL僜乕僗 usbif.vhd 丒丒丒USB僀儞僞僼僃乕僗偺僜乕僗僐乕僪

- UCF僼傽僀儖 main.ucf 丒丒丒僺儞攝抲偲僽儘僢僋RAM偺弶婜抣

忋偺僜乕僗偐傜嵟廔揑偵弌棃忋傞僼傽僀儖偼丄師偺bit僼傽僀儖偱偡丅

丂BIT僼傽僀儖 hasic.bit 丒丒丒僐儞僼傿僌ROM偵彂偒崬傓僼傽僀儖

(XC2S100,僋儘僢僋28.63636MH倸梡)

丂仸28.63636MH倸埲奜偺廃攇悢偱偛巊梡偺応崌偼丄main.vhd偺嵟弶偵偁傞Generic暥傪廋惓偟偰偔偩偝偄丅

HuMANDATA幮惢丄XSP-006-200梡

丂埑揹慺巕偺僒僀僘偑彫偝偄偨傔偐丄掅壒偑傛偄壒偱柭傝傑偣傫丅傾儞僾偲僗僺乕僇乕傪偮側偖偲偲偰傕椙偄壒偑妝偟傔傑偡丅傑偨丄7僙僌儊儞僩LED偵傛偭偰999999傊偉傑偱悢偊傞偙偲偑偱偒傑偡丅

- 僼傽僀儖堦幃丂hasic-xsp006.lzh