丂傗偭偲丄Ver2傪僾儕儞僩婎斅偱偮偔傝傑偟偨丅側傫偩偐嵶挿偔側偭偰偟傑偄傑偟偨丅偝偡偑偵丄僾儕儞僩婎斅偑偁傞偲偡偛偔妝偱偡丅2帪娫掱搙偱偼傫偩晅偗偑偱偒偰偟傑偄傑偡丅偦傟偱傕傗偼傝堦敪偱摦偔偲偄偆偙偲偼擄偟偔偰丄偼傫偩晅偗儈僗傪拲堄怺偔扵偝側偗傟偽側傝傑偣傫丅偦傫側拞偱丄Ver2偺僾儕儞僩婎斅傪嶌偭偨帪偺姶憐傗丄僶僌廋惓傪徯夘偟傑偡丅

丂傗偭偲丄Ver2傪僾儕儞僩婎斅偱偮偔傝傑偟偨丅側傫偩偐嵶挿偔側偭偰偟傑偄傑偟偨丅偝偡偑偵丄僾儕儞僩婎斅偑偁傞偲偡偛偔妝偱偡丅2帪娫掱搙偱偼傫偩晅偗偑偱偒偰偟傑偄傑偡丅偦傟偱傕傗偼傝堦敪偱摦偔偲偄偆偙偲偼擄偟偔偰丄偼傫偩晅偗儈僗傪拲堄怺偔扵偝側偗傟偽側傝傑偣傫丅偦傫側拞偱丄Ver2偺僾儕儞僩婎斅傪嶌偭偨帪偺姶憐傗丄僶僌廋惓傪徯夘偟傑偡丅

丂傗偭偲丄Ver2傪僾儕儞僩婎斅偱偮偔傝傑偟偨丅側傫偩偐嵶挿偔側偭偰偟傑偄傑偟偨丅偝偡偑偵丄僾儕儞僩婎斅偑偁傞偲偡偛偔妝偱偡丅2帪娫掱搙偱偼傫偩晅偗偑偱偒偰偟傑偄傑偡丅偦傟偱傕傗偼傝堦敪偱摦偔偲偄偆偙偲偼擄偟偔偰丄偼傫偩晅偗儈僗傪拲堄怺偔扵偝側偗傟偽側傝傑偣傫丅偦傫側拞偱丄Ver2偺僾儕儞僩婎斅傪嶌偭偨帪偺姶憐傗丄僶僌廋惓傪徯夘偟傑偡丅

丂傗偭偲丄Ver2傪僾儕儞僩婎斅偱偮偔傝傑偟偨丅側傫偩偐嵶挿偔側偭偰偟傑偄傑偟偨丅偝偡偑偵丄僾儕儞僩婎斅偑偁傞偲偡偛偔妝偱偡丅2帪娫掱搙偱偼傫偩晅偗偑偱偒偰偟傑偄傑偡丅偦傟偱傕傗偼傝堦敪偱摦偔偲偄偆偙偲偼擄偟偔偰丄偼傫偩晅偗儈僗傪拲堄怺偔扵偝側偗傟偽側傝傑偣傫丅偦傫側拞偱丄Ver2偺僾儕儞僩婎斅傪嶌偭偨帪偺姶憐傗丄僶僌廋惓傪徯夘偟傑偡丅

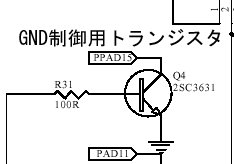

丂廋惓偺屄強偼丄嵍偺夞楬恾偺PPAD15偲偄偆偲偙傠傪PAD16偵偡傟偽惓夝偱偡丅偙偺僩儔儞僕僗僞偼僨僶僀僗偵PIC傪慖戰偟偨偲偒偵ON偵側傝傑偡丅ON偵側傞偲丄PAD16(PIC偺GND僺儞偵懳墳)偐傜揹棳傪堷偒敳偔偺偱丄PIC偺GND偑儐僯僶乕僒儖僾儘僌儔儅偺GND偵堷偐傟傞偙偲偵側傞傢偗偱偡丅

丂廋惓偺屄強偼丄嵍偺夞楬恾偺PPAD15偲偄偆偲偙傠傪PAD16偵偡傟偽惓夝偱偡丅偙偺僩儔儞僕僗僞偼僨僶僀僗偵PIC傪慖戰偟偨偲偒偵ON偵側傝傑偡丅ON偵側傞偲丄PAD16(PIC偺GND僺儞偵懳墳)偐傜揹棳傪堷偒敳偔偺偱丄PIC偺GND偑儐僯僶乕僒儖僾儘僌儔儅偺GND偵堷偐傟傞偙偲偵側傞傢偗偱偡丅

丂婎斅偺廋惓売強1売強栚偼丄40僺儞僜働僢僩偺15斣偲16斣偺僺儞偺晹暘偱偡丅

恾柺偼婎斅傪棤偐傜傒偨奊偱偡丅

偙偺奊偺僶僣報偺晹暘傪僇僢僞乕僫僀僼側偳偱愗抐偟偰偔偩偝偄丅

偦傟偐傜丄椢偺慄偱彂偄偨晹暘傪僕儏儞僼儘儞慄側偳偱愙懕偟偰偔偩偝偄丅

2SC3419偼丄4偮暲傫偩僩儔儞僕僗僞偺棤偐傜尒偰堦斣塃懁偱偡丅

懠偺3偮偼2SC1815偱摦嶌偟傑偡丅

丂婎斅偺廋惓売強1売強栚偼丄40僺儞僜働僢僩偺15斣偲16斣偺僺儞偺晹暘偱偡丅

恾柺偼婎斅傪棤偐傜傒偨奊偱偡丅

偙偺奊偺僶僣報偺晹暘傪僇僢僞乕僫僀僼側偳偱愗抐偟偰偔偩偝偄丅

偦傟偐傜丄椢偺慄偱彂偄偨晹暘傪僕儏儞僼儘儞慄側偳偱愙懕偟偰偔偩偝偄丅

2SC3419偼丄4偮暲傫偩僩儔儞僕僗僞偺棤偐傜尒偰堦斣塃懁偱偡丅

懠偺3偮偼2SC1815偱摦嶌偟傑偡丅

丂廋惓偟偨屻偼塃偺幨恀偺傛偆偵側傝傑偡丅

丂廋惓偟偨屻偼塃偺幨恀偺傛偆偵側傝傑偡丅

丂偙偲傕偁傠偆偵丄崅僀儞僺乕僟儞僗偺攝慄傪堷偒夞偟偰偟傑偄傑偟偨丅偦傟偩偗偑尨場偐偳偆偐傢偐傝傑偣傫偑丄VCC梡偺揹尮惂屼僆儁傾儞僾偺摦嶌偑旕忢偵晄埨掕偱偡丅VPP揹埑偺敪惗偺曽偵偼慡偔栤戣偁傝傑偣傫丅

丂偙偲傕偁傠偆偵丄崅僀儞僺乕僟儞僗偺攝慄傪堷偒夞偟偰偟傑偄傑偟偨丅偦傟偩偗偑尨場偐偳偆偐傢偐傝傑偣傫偑丄VCC梡偺揹尮惂屼僆儁傾儞僾偺摦嶌偑旕忢偵晄埨掕偱偡丅VPP揹埑偺敪惗偺曽偵偼慡偔栤戣偁傝傑偣傫丅

丂VCC揹埑惂屼梡僩儔儞僕僗僞偺儀乕僗偵峴偔怣崋(僆儁傾儞僾偺弌椡)偑敪怳偟偰偟傑偄傑偡丅偱傕丄偄偮傕敪怳偡傞偺偱偼側偔丄EPROM偺2764乣27512偵彂偒偙傒偡傞偲偒偩偗敪怳偟傑偡丅弌偰偒偨VCCDEV揹埑偵偼傎偲傫偳塭嬁偟傑偣傫偑丄婥枴埆偄偱偡丅

丂偄傑丄徻偟偄尨場偲懳嶔傪峫偊偰偄傑偡偑丄偲傝偁偊偢丄VCCDEV揹尮傪2K偺掞峈偲1K偺掞峈偱暘埑偟偰僆儁傾儞僾偵栠偟偰偄傞晹暘偺嫍棧傪嬻拞攝慄偱抁偔偡傞傛偆偵偟傑偟偨偑丄姰慡偵偼捈傝傑偣傫丅

丂偲偐偄偆僩儔儞僕僗僞傪巊偆傛偆偵夞楬恾傗晹昳昞偵彂偄偰偄傑偡偑丄偙偺僩儔儞僕僗僞偼擖庤崲擄偵側偭偰偄傞偙偲偑傢偐傝傑偟偨丅偲傝偁偊偢丄2SC3631偺偐傢傝偵埨壙側2SC1815傪巊偄傑偟偨偑丄EPROM傗SEEPROM丄PIC偼栤戣側偔撉傒彂偒偱偒偰偄傑偡丅偨偩丄GAL偑偳偆傕偆傑偔峴偒傑偣傫丅尨場偼偍偦傜偔Vce(sat)偱偡丅戙懼昳傪偳偆偡傞偐偼専摙拞偱偡丅

丂偲偐偄偆僩儔儞僕僗僞傪巊偆傛偆偵夞楬恾傗晹昳昞偵彂偄偰偄傑偡偑丄偙偺僩儔儞僕僗僞偼擖庤崲擄偵側偭偰偄傞偙偲偑傢偐傝傑偟偨丅偲傝偁偊偢丄2SC3631偺偐傢傝偵埨壙側2SC1815傪巊偄傑偟偨偑丄EPROM傗SEEPROM丄PIC偼栤戣側偔撉傒彂偒偱偒偰偄傑偡丅偨偩丄GAL偑偳偆傕偆傑偔峴偒傑偣傫丅尨場偼偍偦傜偔Vce(sat)偱偡丅戙懼昳傪偳偆偡傞偐偼専摙拞偱偡丅

丂偲傝偁偊偢丄Q4,Q5,Q6偼2SC1815偱丄Q7偼2SC3419偱OK偱偡丅

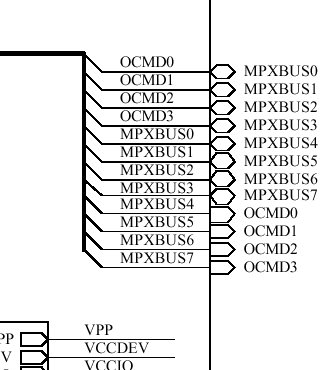

丂嵟戝偺儈僗偼丄嵍偺夞楬恾拞偺偙傟偱偡丅偙偺傑傑偮偔偭偰偟傑偄傑偟偨丅巇曽偑側偄偺偱丄CPLD(XMP1)偺僺儞攝抲傪夞楬恾偵揔崌偡傞傛偆偵偢傜偡偙偲偱夝寛偟傑偟偨丅偮傑傝丄攝慄偵偼堦愗曄峏偡傞偙偲側偔丄僾儕儞僩婎斅偺儈僗偵崌傢偣偰CPLD偺僺儞攝抲傪曄峏偟偨傢偗偱偡丅偙偺傛偆側僶僌僼傿僢僋僗偑偱偒傞偺傕CPLD側傜偱偼偺棙揰偱偡丅

丂嵟戝偺儈僗偼丄嵍偺夞楬恾拞偺偙傟偱偡丅偙偺傑傑偮偔偭偰偟傑偄傑偟偨丅巇曽偑側偄偺偱丄CPLD(XMP1)偺僺儞攝抲傪夞楬恾偵揔崌偡傞傛偆偵偢傜偡偙偲偱夝寛偟傑偟偨丅偮傑傝丄攝慄偵偼堦愗曄峏偡傞偙偲側偔丄僾儕儞僩婎斅偺儈僗偵崌傢偣偰CPLD偺僺儞攝抲傪曄峏偟偨傢偗偱偡丅偙偺傛偆側僶僌僼傿僢僋僗偑偱偒傞偺傕CPLD側傜偱偼偺棙揰偱偡丅

丂偙傟偼丄僔儑僢僩僉僶儕傾僟僀僆乕僪偱偡丅SC59偲偄偆彫偝側昞柺幚憰僷僢働乕僕偱偡偺偱丄偼傫偩晅偗偼偪傚偭偲丄擄偟偄偐傕偟傟傑偣傫丅偱傕丄弴曽岦揹埑崀壓偑偲偰傕彫偝偐偭偨偺偱丄巊傢偢偵偼偄傜傟傑偣傫偱偟偨丅

丂偙傟偼丄僔儑僢僩僉僶儕傾僟僀僆乕僪偱偡丅SC59偲偄偆彫偝側昞柺幚憰僷僢働乕僕偱偡偺偱丄偼傫偩晅偗偼偪傚偭偲丄擄偟偄偐傕偟傟傑偣傫丅偱傕丄弴曽岦揹埑崀壓偑偲偰傕彫偝偐偭偨偺偱丄巊傢偢偵偼偄傜傟傑偣傫偱偟偨丅

丂0.5mm偲偐偄偆攝慄偼偁傝傑偣傫偑丄僺儞偲僺儞偺娫偵攝慄偑堦杮憱偭偰偄傞応崌傗丄僺儞偺偡偖偦偽傪攝慄偑捠偭偰偄傞応崌偑懡偄偱偡丅偙偺傛偆側売強偱僽儕僢僕偑昿敪偡傞偺偱丄拲堄偑昁梫偱偡丅巹偼3売強僽儕僢僕偟偰偟傑偄傑偟偨丅偦偺偆偪丄抳柦揑側僽儕僢僕偵傛偭偰CPLD偺弌椡僺儞傪堦屄懝彎偟偰偟傑偭偨傛偆偱偡丅

丂0.5mm偲偐偄偆攝慄偼偁傝傑偣傫偑丄僺儞偲僺儞偺娫偵攝慄偑堦杮憱偭偰偄傞応崌傗丄僺儞偺偡偖偦偽傪攝慄偑捠偭偰偄傞応崌偑懡偄偱偡丅偙偺傛偆側売強偱僽儕僢僕偑昿敪偡傞偺偱丄拲堄偑昁梫偱偡丅巹偼3売強僽儕僢僕偟偰偟傑偄傑偟偨丅偦偺偆偪丄抳柦揑側僽儕僢僕偵傛偭偰CPLD偺弌椡僺儞傪堦屄懝彎偟偰偟傑偭偨傛偆偱偡丅