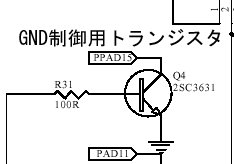

丒塃偺恾偱丄PPAD15偲側偭偰偄傞売強偼PPAD16偑惓夝偱偡丅偮傑傝丄Q4偺僐儗僋僞偼40僺儞僜働僢僩偺16斣僺儞偵愙懕偝傟傑偡丅

丒塃偺恾偱丄PPAD15偲側偭偰偄傞売強偼PPAD16偑惓夝偱偡丅偮傑傝丄Q4偺僐儗僋僞偼40僺儞僜働僢僩偺16斣僺儞偵愙懕偝傟傑偡丅

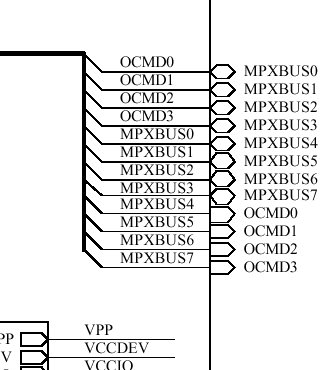

丂崱夞偺夞楬恾偱嵟戝偺娫堘偄偑偙傟偱偡丅傒偰偺捠傝丄MPXBUS[7:0]偲OCMD[3:0]偺愙懕偑夞楬恾忋偱娫堘偭偰偄傑偡丅偦偺偨傔僾儕儞僩婎斅偺僷僞乕儞傕娫堘偭偰偟傑偄傑偟偨丅偙傟偼丄CPLD偺僺儞攝抲傪偙偺夞楬偵揔崌偡傞傛偆偵曄偊傞偙偲偱懳張偱偒傑偟偨丅偦偺偨傔丄Ver2梡偺僾儕儞僩婎斅傪巊偆応崌偵偼CPLD1(XMP1)偵Ver2梡偺CPLD傪巊梡偟側偗傟偽側傜側偔側偭偰偄傑偡丅

丂崱夞偺夞楬恾偱嵟戝偺娫堘偄偑偙傟偱偡丅傒偰偺捠傝丄MPXBUS[7:0]偲OCMD[3:0]偺愙懕偑夞楬恾忋偱娫堘偭偰偄傑偡丅偦偺偨傔僾儕儞僩婎斅偺僷僞乕儞傕娫堘偭偰偟傑偄傑偟偨丅偙傟偼丄CPLD偺僺儞攝抲傪偙偺夞楬偵揔崌偡傞傛偆偵曄偊傞偙偲偱懳張偱偒傑偟偨丅偦偺偨傔丄Ver2梡偺僾儕儞僩婎斅傪巊偆応崌偵偼CPLD1(XMP1)偵Ver2梡偺CPLD傪巊梡偟側偗傟偽側傜側偔側偭偰偄傑偡丅