| CPLDの構造 |

|---|

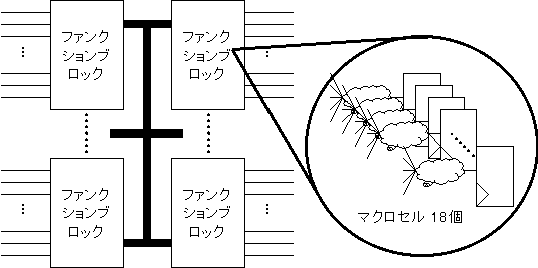

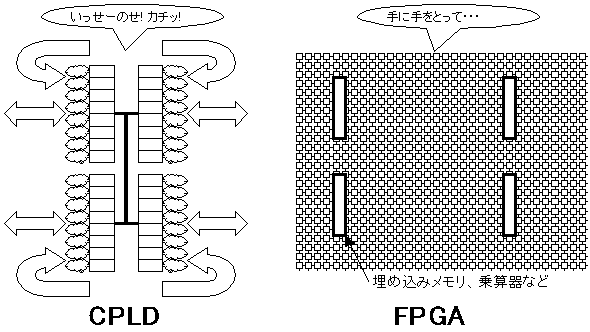

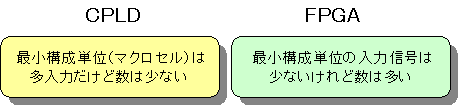

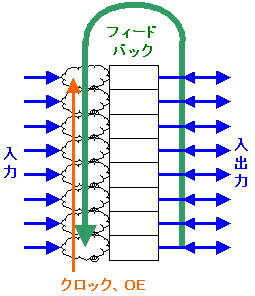

XILINXのCPLDは下の図のような構造をしています。

ファンクションブロックは18本の入出力端子を持つブロックで、

CPLD内では複数のファンクションブロックが太い配線で接続されています。

そしてファンクションブロックは18個のマクロセルから構成されています。

一見して、TTLで組んだデジタル回路とはぜんぜん違います。このような回路で従来のTTL回路を置き換えできるのでしょうか?

|

| TTL時代の回路構成 |

|---|

|

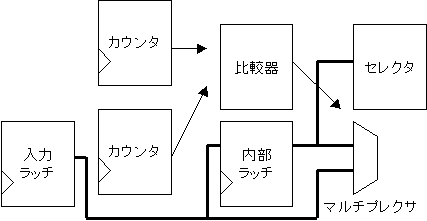

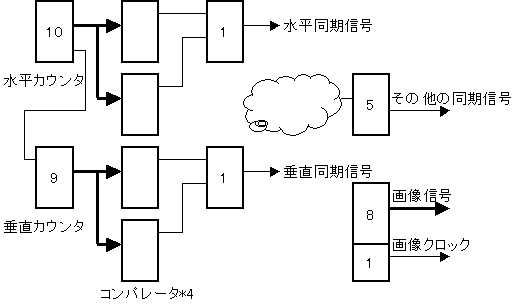

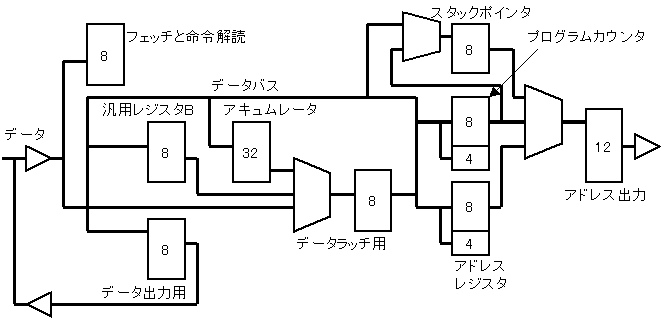

まず、TTL時代にはどのような設計がおこなわれていたでしょうか?TTL ICを使った回路では、カウンタやラッチ、コンパレータ、セレクタ、プライオリティーエンコーダ、マルチプレクサなど、中規模の機能を持ったICを組み合わせて回路を構成していましました。

|

| 組み合わせ回路とは |

|---|

組み合わせ回路とはコンパレータやデコーダ、マルチプレクサなど、クロックを必要とせずに、入力が決まれば瞬時に結果が得られるものです。そのような回路を組み合わせ回路といい、組み合わせ回路をループせずに組み合わせた回路も、また組み合わせ回路となるという性質があります。

たとえば10個の74HC138を組み合わせて作った複雑なアドレス選択回路も、入力が決まれば瞬時に出力が決まります。与えられた数値を11倍して5を足す回路も、入力が決まれば瞬時に出力が決まります。このような回路も組み合わせ回路です。

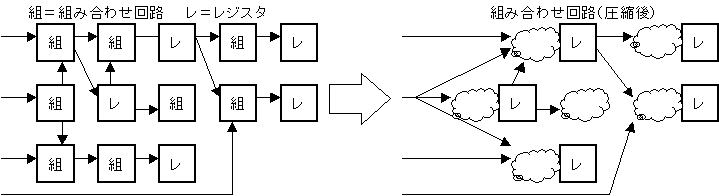

ところで、組み合わせ回路を複数集めると、普通は論理的な冗長性が生じます。この冗長性は圧縮することができます。次の図は複数の組み合わせ回路とレジスタで構成されたTTL回路の例で、圧縮してしまうことで残った組み合わせ回路とレジスタだけになる様子をあらわしています。

圧縮してできた組み合わせ回路は、ANDとORとNOTの塊のような回路で、これをTTLの標準ロジックを集めて作るのは手間がかかりすぎるので普通はやりません。

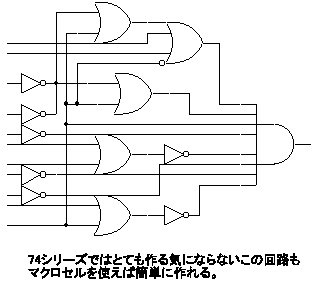

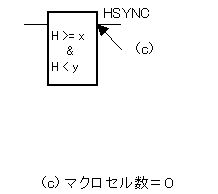

下の図は11ビットの入力から1ビットを出力する簡単な組み合わせ回路の例ですが、74シリーズのICでこのような回路を作る気にはなれません。このような組み合わせ回路を汎用のTTLロジックで作ることは現実的ではなかったので、マルチプレクサやエンコーダ、コンパレータなどの機能を持ったICが街で売られていたわけです。

|

| マクロセルとは |

|---|

マクロセルはCPLDを構成する基本単位で、汎用の組み合わせ回路と1ビットのレジスタ(フリップフロップ)で構成されています。汎用の組み合わせ回路は、ANDやOR、NOTそしてXORを自由にプログラミングでき、先ほどのような面倒な回路も、はんだ付けをすることなしに、作れてしまいます。

TTL回路の圧縮でもそうですが、組み合わせ回路の先にはレジスタ型の回路がつながる場合が多いので、マクロセルは組み合わせ回路とレジスタをセットにした構造になっています。

CPLDは、組み合わせ回路が適切にプログラムされた数多くのマクロセルをつなぎ合わせて作る回路というわけです。

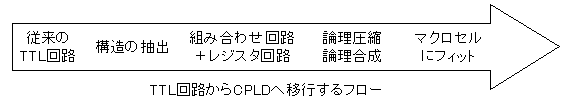

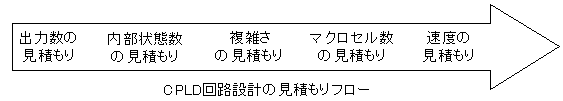

CPLD回路設計の最も重要なステップは、マクロセルにフィットさせることです。CPLD設計の流れを下の図に示しますが、人間がおこなう作業は元にするTTL回路の本質を見極めて構造を抽出するところです。それ以外の処理はツールが自動でおこなってくれます。

マクロセルの構造を意識しなくてもツールはそれなりにフィットしてくれますが、チップの使用率が100%近いような極限状態や、チップの最大速度を出そうと思うならばマクロセルの構造に気を使った設計をしなければなりません。

|

| 組み合わせ回路とROMの違い |

|---|

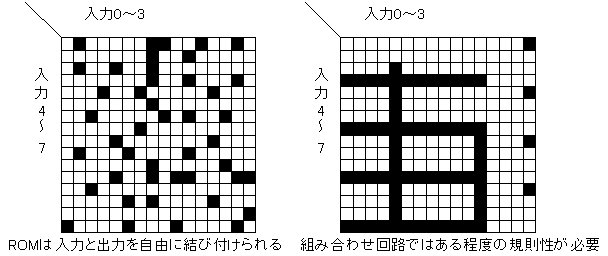

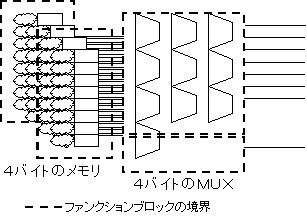

組み合わせ回路とROMの違いについても簡単に触れておきます。マクロセル内の組み合わせ回路は、18ビットの入力から1ビットの出力を得るためのもので、その点だけみればROMの動作に似ています。しかし、18ビットアドレスのROMでは262144種類の情報は完全にランダムに設定できるのですが、組み合わせ回路はそうではありません。ある程度の「簡単さ」が必要になります。

下の図はその「簡単さ」を理解していただくためのイメージ図です。図を書く都合で8ビット入力1ビット出力の回路を組んだ場合を例に説明します。ROMでは入力と出力を完全に自由に対応づけできますが、CPLDでは右の図のような規則性が要求されます。

このような制限があるにもかかわらず、CPLDが世の中のかなりの回路をフィットできるのは、実際のアプリケーションで求められている回路、上図の右側の図のような規則性を備えているからに他なりません。

その「簡単さ」は、既存のTTLの組み合わせ回路を圧縮して作られたような回路であれば満たしていますが、8*8ビット乗算器の結果の10ビット目などというのは複雑過ぎて作ることができません。このような場合はFPGAを使うことになります。

なおFPGAでは、回路の構成単位はマクロセルではなく、小規模RAMです。このRAMはユーザーが自由にプログラムできるのですが、回路から見ればROMのようなものですから、上の図の左側のように任意のロジックを作ることができるわけです。FPGAはとても自由度が高いのです。

最後になりましたが、マクロセルのレジスタは使用しないこともできます。レジスタを使用しなければ、組み合わせ回路の結果が直接出力されます。

|

TOPページへ戻る

TOPページへ戻る 電子回路の豆知識

電子回路の豆知識 御意見、御感想は

御意見、御感想は

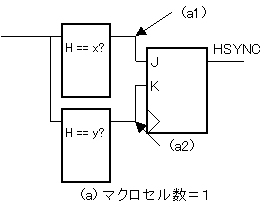

最初のパターンでは、左の図に示したようにコンパレータを2つとJKフリップフロップを1つ使います。

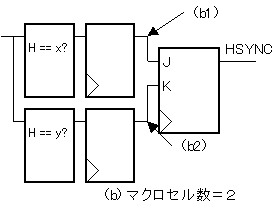

最初のパターンでは、左の図に示したようにコンパレータを2つとJKフリップフロップを1つ使います。 次の例は2つのコンパレータの出力を一度レジスタに通すものです。この方法ですと、2つのレジスタは互いにくっついて圧縮されることはありませんが、マクロセルを3つ消費します。また、組み合わせ回路は純粋なコンパレータのままなので、動作は高速です。

次の例は2つのコンパレータの出力を一度レジスタに通すものです。この方法ですと、2つのレジスタは互いにくっついて圧縮されることはありませんが、マクロセルを3つ消費します。また、組み合わせ回路は純粋なコンパレータのままなので、動作は高速です。 3番目の例は、コンパレータがイコールを比較するのではなく、以上や以下といったものを比較する例です。不等号のコンパレータはイコールを検出するコンパレータよりも複雑になります。

3番目の例は、コンパレータがイコールを比較するのではなく、以上や以下といったものを比較する例です。不等号のコンパレータはイコールを検出するコンパレータよりも複雑になります。

GALで最も有名な16V8では16入力が可能な組み合わせ回路とレジスタが8個入っています。しかしながら16V8は20ピンのICなので、クロックと電源と、汎用の出力トライステートピンによって、ユーザーが使えるピンの数は16本に制限されています。このため、ICの外から見れば8入力8出力のPLDになってしまいます。もちろん8本以上の入力をICの外から得ることはできますが、その場合は大切な出力ピンを入力用として使わなければなりません。

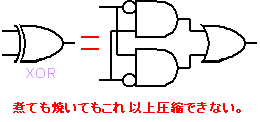

GALで最も有名な16V8では16入力が可能な組み合わせ回路とレジスタが8個入っています。しかしながら16V8は20ピンのICなので、クロックと電源と、汎用の出力トライステートピンによって、ユーザーが使えるピンの数は16本に制限されています。このため、ICの外から見れば8入力8出力のPLDになってしまいます。もちろん8本以上の入力をICの外から得ることはできますが、その場合は大切な出力ピンを入力用として使わなければなりません。 GALでカウンタなどを作るときに最も困るのは、XORの取り扱いです。XORゲートはANDやOR、NOTを組み合わせることで作ることができるゲートなのですが、組み合わせ回路の論理式にXORが出てくるとそれ以上圧縮できないという嫌われ者のゲートなのです。それなのにXORはカウンタや演算回路では頻繁に登場する回路です。

GALでカウンタなどを作るときに最も困るのは、XORの取り扱いです。XORゲートはANDやOR、NOTを組み合わせることで作ることができるゲートなのですが、組み合わせ回路の論理式にXORが出てくるとそれ以上圧縮できないという嫌われ者のゲートなのです。それなのにXORはカウンタや演算回路では頻繁に登場する回路です。