平成14年1月14日朝刊

|

TOPページへ戻る TOPページへ戻る |

| メール |

御意見、御感想は 御意見、御感想はnahitafu at nifty "remove this" dot com |

| Copyright |

|

このWebページ上で紹介したすべての回路、情報、内容に関する著作権は私、なひたふが所有します。無断転載を固く禁じます。 (C)Copyright 1999-2001 Nahitafu |

平成10年2月28日発行.第三種郵便物不認可

| DIMMを自由に使いたいから・・・ Freedim (仮称) |

昨年末の秋葉原での末端価格は64MBあたり1000円でした。これほど安くて大容量なのですから、趣味の工作にも使いたいですね。でも、DIMMの工作は難しいと一般にはいわれています。そこで、DIMMを簡単に扱えるようにするための回路や、ノウハウなどを紹介していこうと思っています。 この工作は以下の内容を中心として実験を進めています。 ・趣味の工作で50MHz超のクロックはOKか? ・TV画面への表示と、オシロを使わないデバッグ方法。 ・SDRAMの詳しい扱い方と、フリーのABEL,VHDLソース。 ・CPUから、パラレルポートから、LANからDIMMにアクセス。 ・高速ロジアナとオシロの作成。 |

| 回路の目的 |

|---|

| 高速で安価、大容量であるDIMMを、趣味の工作の手の届く範囲にすることです。そして、その回路図やCPLD、FPGAのソースをフリーで配布することです。 平成14年現在、秋葉原でも気軽にXILINX CPLDが購入できるようになりました。しかしながらFPGAはいまだに購入することはできません。FPGAは次々とパワフルな新製品が発表されているのに、我々趣味人はCPLDを使わなければならないのでしょうか。 それなら、CPLDを限界まで使って、FPGAに匹敵するようなものを作ろうではありませんか!! |

| 作るもの |

|

SDRAMを使った大容量高速ロジックアナライザを目指します。入力は32chで100MHz。 まずは万能基板で実験機を作ります。でも万能基板ではそれほど性能がでないでしょうから、今回は50MHzで動かします。 |

| DIMMのための最小構成の考察 |

|---|

| この節では、DIMMを制御するために、もっとも小さな規模で、遅くても許されるデバイスは何かということを探っていきます。 |

| CPLDは何個必要か? |

| XC95108-15PC84Cが最低2個必要です。 ひとつはアドレスと制御信号の生成に使います。もうひとつはデータ信号をラッチしたり、セレクトするに使います。ただし、これは64bitあるDIMMを半分しか使わず、32bitとした場合です。もし、DIMMを64bitでフル活用したい場合には、3個必要になります。 理由を簡単に説明します。XC95108にはマクロセルが108個入っています。それは、1ビットのレジスタが108個あることを意味しています。しかし、108個のレジスタの中でICの外に信号を取り出せるレジスタは70個くらいしかありません。なぜならICのパッケージが84ピンだからです。もし、DIMMと64ビットのデータをひとつのCPLDで制御したい場合には、144ピンや208ピンもあるようなQFPパッケージのCPLDを使わなければなりません。でもそれは秋葉原には売っていません。 楽観的に考えれば、XC95108-15PC84Cでも、2個使えばDIMMを制御できるのですから嬉しいですね。 |

| 必要なCPLDの速度は? |

|

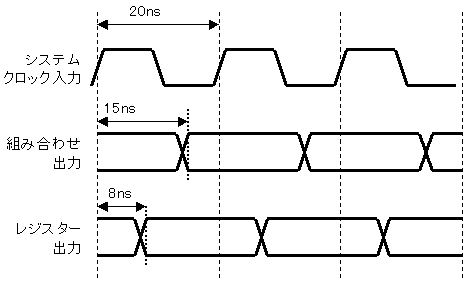

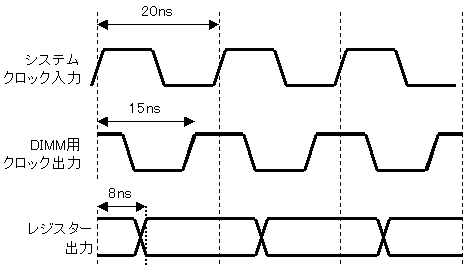

DIMMには50MHzのクロックを与えてアクセスすることを考えます。100MHzや133MHzというのは、さすがに万能基板の上で引き回すのは難しいと考えたからです。私は50MHzを少し超えた回路の設計をおこなったことがありますが、50MHz付近ではそれほど難しくは感じませんでした。 クロック周波数50MHzではクロックの周期が20nsになります。これは結構速い速度だとは思いますが、この周期に対してXC95108-15PC84Cの出力は間に合うのでしょうか。  この図は、XC95108-15PC84Cでもっとも速い回路を作った場合の出力タイミングです。 組み合わせ出力というのは、内部でレジスタを通さない信号です。これらの信号は入力から出力まで15.0nsかかります。 レジスタ出力というのは、入力信号を内部のレジスタで処理した出力で、これはクロック入力から8.0ns遅れて出力されます。 DIMMとCPLDが同じクロックで動作するのであれば、このレジスタ出力の変化するタイミングがクロックの立ち上がりよりも数ナノ秒速ければよいわけです。これをセットアップタイムと呼び、通常は1〜3nsくらいです。 もし、DIMMを100MHzで動かすのであれば、クロック周期が10nsになりますから、出力の変化から、次のクロックの立ち上がりまで2nsしかなくなります。こうなるとセットアップタイムが厳しくなり、動作は難しくなります。つまり、秋葉原で売っているXC95108-15ではとても困難なのです。 それでも何とか動かしたい!というのであれば、より高速なCPLDを使うか、DIMMに与えるクロックのタイミングを5nsくらい遅らせてやればよいのですが、クロックのタイミングを変えると、設計はとてもややこしくなるのでお勧めできません。 それ以前に、XC95108-15PC84Cは最高動作周波数が54MHz程度なので、100MHzは無理でした。 |

| クロック |

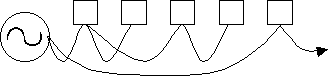

パソコンのマザーボードなどで、右の図のようなクネクネした配線を見たことはありませんか?

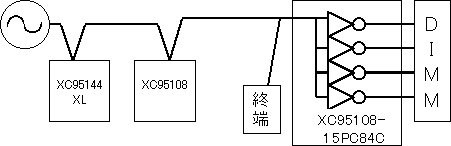

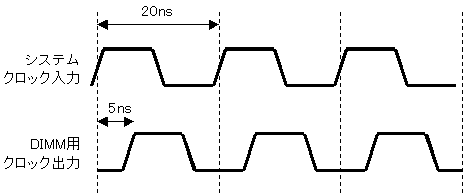

パソコンのマザーボードなどで、右の図のようなクネクネした配線を見たことはありませんか?これは、配線の長さをそろえるための工夫で、電気信号が到達する時間をそろえるためにこのように曲がりくねっているのです。 このように、高速なデジタル回路では電気信号の伝わる速さまで考慮して設計しなければ、本当に信頼性の高いものは作ることはできません。特にクロック信号は敏感であるといわれ、クロック信号だけは他の信号よりも丁寧に扱わなければいけないと、一般にはいわれています。 たとえば、クロック線を、次のように配線をすることは(16MHzか20MHzくらいよりも)高い周波数の回路ではタブーです。  少なくとも、クロックは一筆書きにして最後尾には終端抵抗を入れます。できればすべてのIC用に別々のドライバを用意して等長配線するのが理想です。でも、そうはいっていられないのも現実です。 DIMMには4本のクロック入力がありますが、これらのクロック入力は一筆書きでつないではいけません。タイミングのそろった4本のクロックを別々のドライバで作り出し、等長配線するのがベストです。 クロックを分配するには、専用のクロックドライバというICが売られています。でも、そんなICは秋葉原では見たことがありません。本実験回路では、クロックドライバを用意する代わりに、DIMMに与えるクロックをCPLDで分配することにしました。この際に使用したCPLDは、やっぱりXC95108-15PC84Cです。  XC95108の中で、クロックの信号を反転させていることに注目してください。XC95108-15で入力信号を単純に出力するための遅延時間は15nsでした。論理を反転させているため、位相が180度かわることになるので、時間でいえば10ns遅れる(あるいは進む)ことになります。XC95108がDIMMへ出力するクロックは、システムクロックから25nsあるいは5ns遅れたものが出力されます。(25nsの遅れは5nsの遅れと同じです。)  DIMMのセットアップタイムに、さらに5nsの余裕ができました。でも、これは同期式設計としてはあまりよいことではありません。DIMMが出力するデータ信号のタイミングも後ろに5nsずれることになるのですから。 |

| 本機の構成 |

|---|

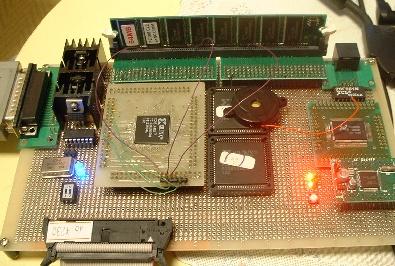

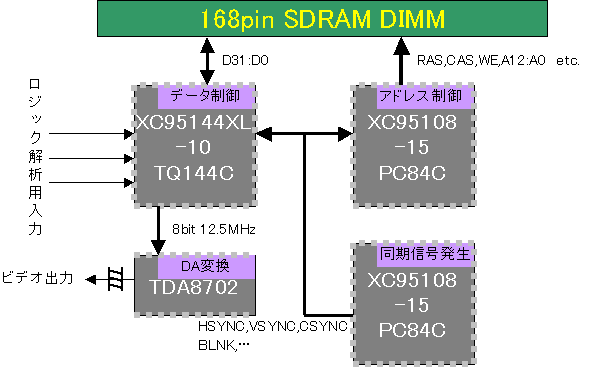

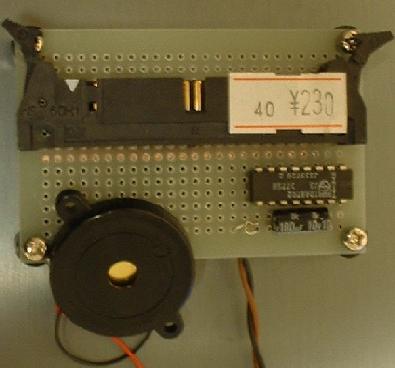

まずは、DIMMを扱った実験を行うために、次に示すような回路を作成しました。

DIMM実験機の構成

本機には3つのCPLDがあります。ひとつはただひたすら同期信号を発生させるだけのCPLDです。このCPLDにはインターレース付きのコンポジット同期信号をも発生させる回路を組み込んでいます。 DIMMにRAS信号やCAS信号、WEやバンク・行・列アドレスを与えるのは、別のCPLDの役割です。このCPLDは同期信号を見ながら、リフレッシュや読み出しなどの動作を行っています。 DIMMからデータ信号を受け取り、それを加工してDAコンバータに渡すのは、XC95144XLの役割です。XC95144XLという比較的大規模なCPLDを使わなくても、XC95108でも十分ですが、好みにより144XLを使いました。 これら、3つのCPLDはすべて同一の50MHzクロックに同期して動いています。  DIMM実験機の写真 H8とLANはまだ使っていません。 これとは別基板に、高速DAコンバータを載せています。目的は回路のデバッグ用です。私は高速オシロやロジックアナライザを持っていないので、本機の回路にロジアナとしての機能を備えさせて、波形をテレビ画面に表示させながらデバッグを行うためです。 |

| ソースの公開 |

|---|

|

使用したCPLDのソースはGPLの元で公開します。ただし、やっと動いた非常に汚いソースです。あまりに汚すぎて恥ずかしいので、近いうちに予告なしに修正します。このソースを使って、オリジナルなものを作成、公開、販売しても構いませんが、礼儀として参照した旨は記してください。 なお、今の段階ではソースはABELです。なぜならVHDLはコンパイルに時間がかかるから嫌なのです。でもFreedimが完成した暁には、より多くの人に使っていただくためにVHDLに移植します。 |

| 回路図 |

| 回路図は書いていないので、出せません。基板を起こすときになったら書きます。それまではCPLDの同じ名前のピン同士をつないでください。 |

| アドレス制御用CPLDのソース |

|

dimmpa.npl Webpack用プロジェクトファイル dimmpa.abl ABELソース dimmpa.ucf ピン配置定義ファイル |

| 同期信号発生用CPLDのソース |

|

dimmpb.npl Webpack用プロジェクトファイル dimmpb.abl ABELソース dimmpb.ucf ピン配置定義ファイル csync50.abl 同期信号発生用ABELソース |

| データ制御用CPLDのソース |

|

dimmpc.npl Webpack用プロジェクトファイル dimmpc.abl ABELソース dimmpc.ucf ピン配置定義ファイル |

|

制御ソフトです。 Project1.bpr Borland C++Builder用プロジェクトファイル Project1.cpp Borland C++Builder用 C++ソース Project1.res Borland C++Builder用 リソースファイル Unit1.cpp Borland C++Builder用 C++ソース Unit1.h Borland C++Builder用 C++ソース Unit1.dfm フォーム定義ファイル |

| 進捗状況 |

|---|

DIMMに、画像を記録させ、テレビの画面に表示させた写真です。

元の画像はカラーなのですが、映っている画像が白黒なため、カラーでお見せできないのが残念です。これは私が作った自家製のラー油です。本当は唐辛子の真っ赤な色をしています。  これもカラーでお見せできないのが残念です。この画像は新橋にある、とても辛い四川料理のお店で、火鍋を食べた時の写真をテレビに表示させています。これも白黒なのが残念です。 ちなみに火鍋というのは、つゆに唐辛子がいっぱい入って、真っ赤になっている鍋料理なのですが、これがとても辛くておいしいんです。あまりに辛すぎるためなのか、なかなか火鍋が食べられるお店はありません。 |

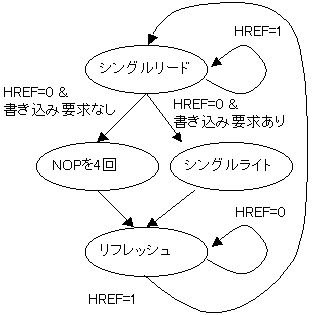

| ステートマシン |

画像を表示させるためのステートマシンは、下の図のように動作しています。 HREFというのは、画像を画面に表示する期間にHになる信号です。画像表示期間にはシングルリードを繰り返してそれをDAコンバータに送り、TV画面に表示させています。HREFが0になった時、すなわち水平帰線期間に入ると、1バイトだけ書きこみをおこないます。ただし、書きこみ要求がない場合には、書きこみは行いません。水平帰線期間の最中はひたすらリフレッシュをおこないます。 ステートマシンの詳しい動作は、上で公開したソース(dimmpa.abl)を読んでください。 |

| 隘路(あいろ) |

|---|

| 隘路とは、物事を進めていくうちに突き当たった壁です。Freedimの開発にはさまざまな隘路がありました。そんな隘路を少しづつ書いていきます。 |

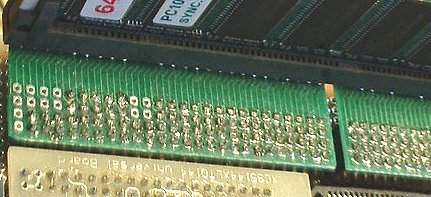

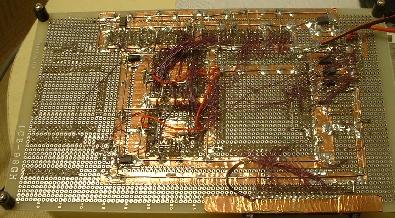

| DIMMのソケットと基板 |

|

最初につまづいたのが、DIMMのソケットをさす基板です。DIMMのソケットは千石に200円で売っていますが、もちろん、これが素直にささる万能基板はありません。 ちなみにこのソケットの足は2.54mmの4列千鳥です。 サンハヤトの変換基板を探していたら、4列の千鳥を通常の4列に変換する基板がありました。一個780円です。残念ながら、これには168ピンもの数のピンがありませんでした。 幸いなことに、DIMMは真ん中(39,40ピンの間)にピンがない場所があります。そこを利用して、2枚のサンハヤトの基板を使うことにしました。  まずはじめに、サンハヤトの変換基板を、のこぎりで適切な大きさに切ります。そこに秋月で買ってきた2列のピンヘッダーのメスをいっぱい挿し、万能基板側にはそれに勘合するようにピンヘッダのオスを挿します。そして、あとは504箇所はんだ付けすれば完成です。 |

| 読み出しが、たまに失敗する |

|

あるアドレスから読み出しを行った場合、必ず失敗するという現象が発生しました。これをテレビの画面でみると、決まった位置に白や黒の点が出るように見えました。 最初は、XC95108でDIMM用クロックを生成するときに、分配回路をインバータではなく単なるバッファとしていたため、次に示すようなタイミングになっていたと思われます。  DIMM用のクロックが遷移するのが、システムクロックから15ns後です。RASやCASやアドレスに使われているレジスタ出力が遷移するのは、システムクロックから8ns後です。だからセットアップ時間は間に合うはずです。しかしごく稀に、決まったアドレスでDIMMから正しい値を読み出せなかったのです。 結局、現在のようにXC95108の中身をインバータにしたら解決しましたが、原因はいまだに不明です。 |

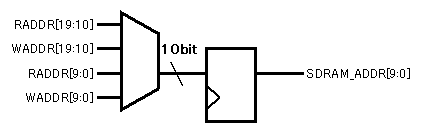

| マルチプレクサ |

|

本回路は、DIMMに書きこみをおこなうためのアドレスと、読み出しをおこなうためのアドレスカウンタを別々に持っています。アドレスカウンタはそれぞれが24bit構成です。RASとCASアドレスを切り替えるための、マルチプレクサで多少苦労しました。 実験していると、CASアドレスがうまく切り替わっていないことがわかりました。常に特定のビットが0に固定されているのです。WebPackの生成したタイミングレポートを見ると、そのピンだけ遅延時間が25nsくらいになっています。本来ならクロックから8nsで出てほしい信号なのに、こんなに遅延が多くては使い物になりません。 その原因を調べてみると、「ファンクションブロックが溢れたから、あなたの指定したとおりには配置できなかった。よそのファンクションブロックを経由するね。」というWarningメッセージが出ていました。 WebPackは、配置できないほど密度の高い設計(難しいことではない)をすると、このメッセージのように、よそのファンクションブロックを経由して配置配線をおこなってくれます。しかしそうなると、動作速度が急激に下がりますので、手作業で回路の密度を下げなければなりません。 具体的にいえば、どのような回路が問題だったかというと、  40本のアドレス信号を、10本に束ねるマルチプレクサです。XILINXのCPLDはひとつのファンクションブロックに36本の信号までしか入れることができません。ひとつのファンクションブロックをこのアドレス生成回路で占めていたわけではありませんが、ファンクションブロックの入力が足りなくなったため、望んだとおりには配置配線できなかったのです。 そこで、密度を下げるために、パイプライン化しました。CASアドレス(つまり下位のアドレス)は必ずRASアドレスよりも後に入力させるのですから、一度レジスタを通しても構わないはずです。まず、20入力10出力のマルチプレクサを作りレジスタを通します。それを再び30入力10出力のマルチプレクサに入れることで、解決できました。  74何とかの汎用ロジックや、GALを使っていたころには、このような変更はとてもやる気がしないものでしたが、本当にCPLDは便利だなと感じさせられる一瞬です。 |

| デバッグの方法 |

|

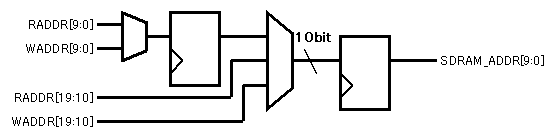

私はこの装置をデバッグする際に、オシロスコープやロジアナを使わないという方針でデバッグを行うことにしました。理由はともかく、どのようにすればロジック回路をオシロやロジアナを使わずにできるでしょうか? まず一つ目は、論理式をじっくり眺めることです。これで大抵のバグは発見できます。でも、もっと根本的な問題としてクロックが止まっていたり、必要なイネーブル信号が止まっているためにまったく動いていないなんていうことも考えられます。 そこで、用意したのが圧電素子!  また、圧電素子はコンデンサとしての機能もあります。電荷が溜まるのです。圧電素子の線をGNDに触れて放電した後で、Hレベルの信号に触れればカチッと音がします。逆にHレベルに充電された状態でLレベルの信号に触れてもカチッと音がします。こうしてHかLかが分かるのです。 圧電素子がひとつあれば、重いオシロを出さなくてもパルスが来ているか、HやLかなどがわかるので、便利ですよね。 それから、上の基板に乗っているICはTDA8702という高速DAコンバータです。この基板はメインの基板とは別基板となっていて、メイン基板から送られたデータを25MHzで8bitDA変換し、それをテレビに直接表示させています。それが次の画像。  今回の工作では、オシロを原則として使わない方針なので、CPLD内部の波形をテレビに表示することにしました。この装置には3つのCPLDがありますが、まだXC95144XLひとつしか使っていません。もちろんCPUも使っていません。ひとつのCPLDだけでこの機能を実現しています。このCPLDには同期信号発生と、グリッド線描画、SDRAM制御信号発生、簡易ロジアナ表示などの機能を持たせています。 なお上の波形は、オートプリチャージ付きの読み込みと書き込み、それからリフレッシュなどの動作を示しています。 さて、波形をテレビに表示させるのはどうやっているのでしょう? あるステートマシンの動作を検証したいとします。メインクロックは50MHzなので、テレビに表示させるドットクロックは12.5MHzになります。すると、1水平ラインの横方向の解像度は650程度になります。50MHzのクロック4個で1ピクセルですから、50MHzの速さで検証したいステートマシンを動かしても速すぎて画面には表示できません。そこで、検証したいステートマシンにウェイトを入れてやり、16クロックや32クロックで一回遷移するようにしました。これによって、グリッドの幅(16ピクセル)にあわせてステートマシンが動いています。 また、水平同期信号を利用してステートマシンをある状態にリセットします。このようにして縦方向の位置を合わせています。 |

| 趣味の工作で50MHz超のクロックはOKか? |

|

可能です。現在、3つのCPLDを50MHzのクロックで駆動していますが、問題なく動いています。しかしながら、高速なクロックはノイズを撒き散らすらしく、インピーダンスの高い信号線にノイズが乗る可能性が高いです。クロックラインからのクロストークが、JTAGなど外部から接続される信号線に乗らないように、外から来る信号には必ずバッファを入れる必要があります。とにかくJTAG信号線はノイズに弱いらしく、回路がビンビン動いているときにはCPLDの書き込みに失敗することが多々あります。CPLの書き込みを確実に成功させるために、私はメインクロックを停止させるスイッチを設けています。 また、クロックの信号には必ず終端させる必要があります。でも、配線が5cmくらいでつながるICがひとつだけならば、終端させなくても動きました。 回路の電源とGNDはベタアースにします。万能基板でベタアースに近いパターンを作る方法は、後日書きます。夜3時、今日はもう眠いです。  |

| XC95108-15は50MHzを超えられるか? |

|

XC95108-15PC84Cは、XC95108で速度が15nsのCPLDです。これは趣味の世界では最もポピュラーといえます。ところが、このCPLDで50MHzを超えることは意外と厳しいのです。このCPLDでは、レジスタの出力が変化するのは、おおよそクロックから8〜9ns後です。また、セットアップタイムが8nsくらいあるので、52MHzくらいが理論的な限界です。 しかし、論理回路が複雑になってくると、CPLD内部にある積項というものが足りなくなるので、あまっている積項を隣のマクロセルやファンクションブロックから借りてくるようになります。こうなると、遅延が増加します。 遅延が20nsを超えると当然ながら50MHzでは動きません。遅延を減らすためには、処理をパイプラインにして、回路を簡略化しなければなりません。今回のDIMM制御用CPLDは51.2MHzでぎりぎりOKでした。 回路が複雑になって、マクロセル2段通さなければならなくなると、最高クロック周波数が激減し、27MHzくらいが限界になります。なんとしてもマクロセル1段で設計しなければなりません。 XC95108-15にとって50MHzというのは、設計テクニックが反映される厳しい点であるといえるでしょう。 |

| CPLDの書き込みは? |

|

もちろん、NAXJPを使っています。純正のダウンロードケーブルと純正の書き込みソフトウェアを使うよりもハードウェアの自由度が高くなるので、とても便利です。プリンタポートをJTAG専用にしてしまわなくてもいいのも大きなメリットでしょう。 ところで、CPLDのアーキテクチャの違いですが、XC95108よりもXC95144XLの方がはるかに高速に書き込みができます。XLシリーズは書き込み前の消去が一括でできるのですが、XC95108はすべてのフューズアドレスに消去コマンドを送らなければならないので、遅いのです。今後はXC95144XLを中心として設計していきたいです。 |

御意見、御感想は

御意見、御感想は