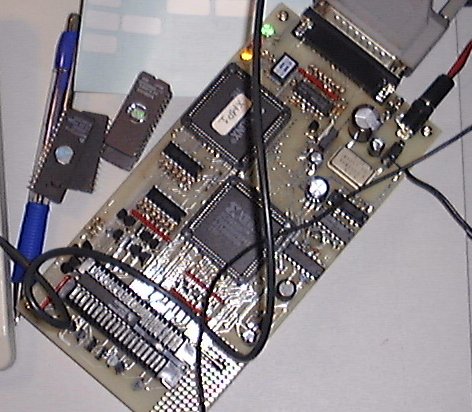

やっと、Ver2をプリント基板でつくりました。なんだか細長くなってしまいました。さすがに、プリント基板があるとすごく楽です。2時間程度ではんだ付けができてしまいます。それでもやはり一発で動くということは難しくて、いままさにデバッグ中の身です。そんな中で、Ver2のプリント基板を作った時の感想や、バグ修正を紹介します。

やっと、Ver2をプリント基板でつくりました。なんだか細長くなってしまいました。さすがに、プリント基板があるとすごく楽です。2時間程度ではんだ付けができてしまいます。それでもやはり一発で動くということは難しくて、いままさにデバッグ中の身です。そんな中で、Ver2のプリント基板を作った時の感想や、バグ修正を紹介します。

やっと、Ver2をプリント基板でつくりました。なんだか細長くなってしまいました。さすがに、プリント基板があるとすごく楽です。2時間程度ではんだ付けができてしまいます。それでもやはり一発で動くということは難しくて、いままさにデバッグ中の身です。そんな中で、Ver2のプリント基板を作った時の感想や、バグ修正を紹介します。

やっと、Ver2をプリント基板でつくりました。なんだか細長くなってしまいました。さすがに、プリント基板があるとすごく楽です。2時間程度ではんだ付けができてしまいます。それでもやはり一発で動くということは難しくて、いままさにデバッグ中の身です。そんな中で、Ver2のプリント基板を作った時の感想や、バグ修正を紹介します。

これは、ショットキバリアダイオードです。SC59という小さな表面実装パッケージですので、はんだ付けはちょっと、難しいかもしれません。でも、順方向電圧降下がとても小さかったので、使わずにはいられませんでした。

これは、ショットキバリアダイオードです。SC59という小さな表面実装パッケージですので、はんだ付けはちょっと、難しいかもしれません。でも、順方向電圧降下がとても小さかったので、使わずにはいられませんでした。

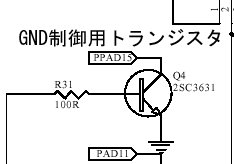

これは、40ピンソケットの15・16番ピンの修正です。16F84ではプログラム電圧(MCLR)(15番)とGND(16番)のピンなのですが、両方とも15番にして設計していました。Ver1の時もそうでしたが、全く気がつきませんでした。パターンカットしてジャンパを飛ばして修正しなければなりません。

これは、40ピンソケットの15・16番ピンの修正です。16F84ではプログラム電圧(MCLR)(15番)とGND(16番)のピンなのですが、両方とも15番にして設計していました。Ver1の時もそうでしたが、全く気がつきませんでした。パターンカットしてジャンパを飛ばして修正しなければなりません。

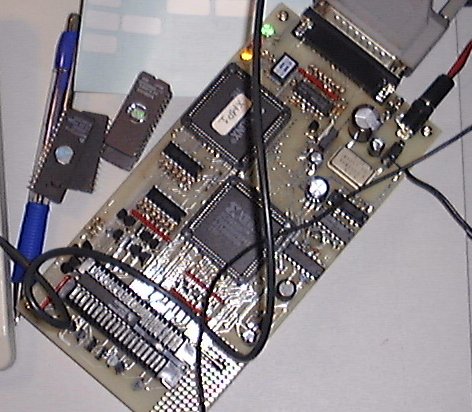

修正の個所は、左の回路図のPPAD15というところをPAD16にすれば正解です。このトランジスタはデバイスにPICを選択したときにONになります。ONになると、PAD16(PICのGNDピンに対応)から電流を引き抜くので、PICのGNDがユニバーサルプログラマのGNDに引かれることになるわけです。

修正の個所は、左の回路図のPPAD15というところをPAD16にすれば正解です。このトランジスタはデバイスにPICを選択したときにONになります。ONになると、PAD16(PICのGNDピンに対応)から電流を引き抜くので、PICのGNDがユニバーサルプログラマのGNDに引かれることになるわけです。

こともあろうに、高インピーダンスの配線を引き回してしまいました。それだけが原因かどうかわかりませんが、VCC用の電源制御オペアンプの動作が非常に不安定です。VPP電圧の発生の方には全く問題ありません。

こともあろうに、高インピーダンスの配線を引き回してしまいました。それだけが原因かどうかわかりませんが、VCC用の電源制御オペアンプの動作が非常に不安定です。VPP電圧の発生の方には全く問題ありません。

VCC電圧制御用トランジスタのベースに行く信号(オペアンプの出力)が発振してしまいます。でも、いつも発振するのではなく、EPROMの2764〜27512に書きこみするときだけ発振します。出てきたVCCDEV電圧にはほとんど影響しませんが、気味悪いです。

いま、詳しい原因と対策を考えていますが、とりあえず、VCCDEV電源を2Kの抵抗と1Kの抵抗で分圧してオペアンプに戻している部分の距離を空中配線で短くするようにしましたが、完全には直りません。

0.5mmとかいう配線はありませんが、ピンとピンの間に配線が一本走っている場合や、ピンのすぐそばを配線が通っている場合が多いです。このような箇所でブリッジが頻発するので、注意が必要です。私は3箇所ブリッジしてしまいました。そのうち、致命的なブリッジによってCPLDの出力ピンを一個損傷してしまったようです。

0.5mmとかいう配線はありませんが、ピンとピンの間に配線が一本走っている場合や、ピンのすぐそばを配線が通っている場合が多いです。このような箇所でブリッジが頻発するので、注意が必要です。私は3箇所ブリッジしてしまいました。そのうち、致命的なブリッジによってCPLDの出力ピンを一個損傷してしまったようです。

とかいうトランジスタを使うように回路図や部品表に書いていますが、このトランジスタは入手困難になっていることがわかりました。とりあえず、2SC3631のかわりに安価な2SC1815を使いましたが、EPROMやSEEPROM、PICは問題なく読み書きできています。ただ、GALがどうもうまく行きません。原因はわかりませんが、このトランジスタかもしれません。代替品をどうするかは検討中です。

とかいうトランジスタを使うように回路図や部品表に書いていますが、このトランジスタは入手困難になっていることがわかりました。とりあえず、2SC3631のかわりに安価な2SC1815を使いましたが、EPROMやSEEPROM、PICは問題なく読み書きできています。ただ、GALがどうもうまく行きません。原因はわかりませんが、このトランジスタかもしれません。代替品をどうするかは検討中です。

すみません。回路図やプリント基板図に指定している色が逆でした。このままでは書きこみ成功したときに赤く光ってしまいます。この写真は間違っている例です。

すみません。回路図やプリント基板図に指定している色が逆でした。このままでは書きこみ成功したときに赤く光ってしまいます。この写真は間違っている例です。

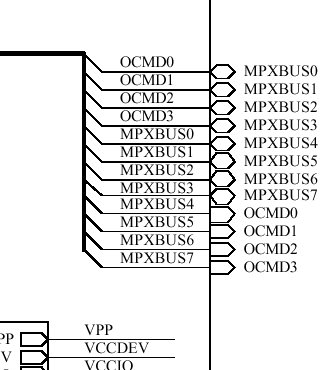

最大のミスは、左の回路図中のこれです。このままつくってしまいました。仕方がないので、CPLD(XMP1)のピン配置を回路図に適合するようにずらすことで解決しました。つまり、配線には一切変更することなく、プリント基板のミスに合わせてCPLDのピン配置を変更したわけです。このようなバグフィックスができるのもCPLDならではの利点です。

最大のミスは、左の回路図中のこれです。このままつくってしまいました。仕方がないので、CPLD(XMP1)のピン配置を回路図に適合するようにずらすことで解決しました。つまり、配線には一切変更することなく、プリント基板のミスに合わせてCPLDのピン配置を変更したわけです。このようなバグフィックスができるのもCPLDならではの利点です。