XILINXのコンフィグには、XC18シリーズなどがよく使われていました。しかしながら、XC18シリーズはコンフィグされる側のFPGAと同程度の価格と、とても高価です。FPGAボードをスタンドアローンで動作させるために、もっと安い方法はないかと考え、いろいろなコンフィグ方法を試してみることにします。

ただし、安いといっても、窓付きの40ピンEPROMなどは使わず、出来るだけ小さく高密度に作ることを目指します。

そのため、ここでは

を目標とします。

平成15年の半ばから、従来のXC18Vシリーズにかわって、新しいXC18Vシリーズが登場しました。この新しいシリーズは製造工場が違うということですが、実は消去に要する時間が大幅に増えているようです。

従来のXC18Vシリーズは1秒以下で消去可能であったのに対し、新バージョンでは15秒を要します。しかしながら、価格は同じです。新旧のバージョンは、JTAGのIDCODEが違うため判別できます。

XC18Vの新バージョンの登場と同じころから、XCFという新しいシリーズが登場しました。これはPlatformFlashという新しいシリーズの製品です。XC18Vとはパッケージが違いますが、使用方法は同じです。

また、XCF08P以上はXC18Vシリーズとは違い、複数のコンフィグを内部に保存しておいて、状況に応じてコンフィグを使い分ける機能や、データの圧縮をサポートしています。

シリアルROMには、I2CやSPI、MicroWireなどいろいろなインタフェース規格があります。秋葉原でも128バイト程度の小規模なものから256kバイトの大きなものまでいろいろなものを入手することができます。

例えば、下記のメーリングリストではSST社の45F010という1MbitシリアルROMとワンチップマイコンを利用してXILINX FPGAのコンフィグを行う例が載っています。

45F010は1個$1.38ととても安いのですが、45F010は独自仕様のインタフェースであるため、製造中止などが発生した場合は代替が利かないというリスクがあります。

そこで、I2CかSPIの一般的なインタフェースで、安価でかつ大容量なシリアルROMを利用してコンフィグすることを考えます。なお、同容量であれば一般的にEEPROMよりもFlashROMの方が安く購入できるのでできればFlashがいいでしょう。

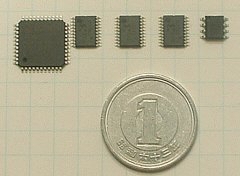

下の図は、各種のシリアルROMの大きさの比較です。0.5mmの方眼の上に乗せて撮影しています。左から順に、XC18V02、XCF01、XCF02、XCF04、そしてSST社のSST25VF020というSPIインタフェースのROMです。

図1 最近のコンフィグ用ROMの大きさ比較

これらの特徴を簡単に比較します。

表1 コンフィグ用ROMの機能と価格

|

種類 |

価格 |

サイズ |

FPGAロード時間 |

ROM書き込み時間 |

余った領域の活用 |

|---|---|---|---|---|---|

|

XC17シリーズ |

△ |

× |

○ |

△ |

× |

|

XC18シリーズ |

× |

× |

○ |

△ |

× |

|

XCFシリーズ |

○ |

○ |

○ |

△ |

× |

|

汎用シリアルROM+マイコン |

○ |

◎ |

△ |

○ |

◎ |

XC18VやXCFをJTAGで書き込む場合、1Mbit品でおよそ20秒から40秒を要します。しかし、汎用シリアルROM+マイコンの組み合わせでは5秒程度でROMへの書き込みは完了します。よって、ROMへの書き込みだけであれば汎用ROMの方が高速です。

しかし、汎用ROMよりも純正ROMの方が読み出し速度は速くできるため、XILINXの純正ROMはFPGAをコンフィグするための時間は0.1秒以下ですが、汎用シリアルROM+マイコンの組み合わせでは3秒程度を要します。

XILINX FPGAのコンフィグ方法には大きく分けて4つあります。

表2 XILINX FPGAのコンフィグモード

|

モード |

説明 |

|---|---|

|

マスターモード |

最も簡単で、使用頻度が多いモードです。 |

|

スレーブモード |

クロックをFPGAの外で発生させ、そのクロックに同期したデータをFPGAに入力します。 |

|

パラレル(SelectMAP)モード |

シリアルモードの8倍の速さでデータを転送できますが、信号線を多く必要とします。 |

|

JTAGモード |

JTAGの信号線を使ってコンフィグを行います。 |

XILINX FPGAには次のようなコンフィグ用の端子があります。

表3 XILINX FPGAコンフィグ用端子の機能

|

端子名 |

入出力 |

機能 |

|---|---|---|

|

M2,M1,M0 |

入力 |

モードを切り替えるために使用します。 |

|

CCLK |

入出力 |

マスターモードのとき出力となり、スレーブモードで入力となります。 |

|

D0/DIN |

入力 |

シリアルデータの入力です。 |

|

DONE |

出力 |

XILINXのコンフィグが完了したときに、Hになります。 |

|

INIT |

出力 |

コンフィグのシーケンスが開始したことをLのパルスで示します。 |

|

PROG |

入力 |

Lのパルスでコンフィグシーケンスを開始します。 |

|

BUSY/DOUT |

出力 |

シリアルデータの出力です。 |

もちろん、全部使う必要はありません。必須なのは、M2、M1、M0、CCLK、DIN、PROGの6本です。

DONEはコンフィグ完了を示す信号です。これをXC18やXCFなどの純正ROMに接続するときは#CEと接続します。純正ROMは#CEがHになると、スタンバイモードに入り、またアドレスカウンタをリセットします。

INITはFPGAがこれからコンフィグを開始することを知らせる信号です。これは通常は純正ROMのOE/#RESETに接続します。この信号がLになるとROMはアドレスカウンタをリセットします。

DOUTは複数のFPGAを接続するときに使用します。

|

|

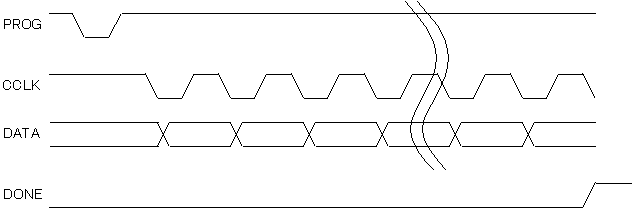

図2 注意を要するコンフィグ方法 |

例えば、FPGAの出力を利用して、自身のコンフィグROMにたいしてJTAGを操作で再書換えするようなアプリケーションを考えます。

FPGAにはコンフィグするためのXC18Vが乗っていて、そのXC18VをFPGAの汎用I/Oから出力するJTAG信号で書き込みを行うというものです。

ROMに対する書き込みは、最初はJTAGケーブルを用いて行い、FPGAがコンフィグした後の再書換えは、FPGA経由で自己書換えすることができます。

FPGAはコンフィグ前だから全てのピンがハイインピーダンスだからJTAGから書き込みができるだろうという考え方です。

このような場合注意しなければならないことは、FPGAのI/Oの中にはコンフィグ前にハイインピーダンスとはならないピンがいくつかあることです。

例えば、DONEやINITといったピンはコンフィグ後にはユーザI/Oとして使うことができるピンですが、電源投入直度は出力となっています。同様にDOUT/BUSYというピンは、使用する機会が少ないためコンフィグ用信号であることを忘れられがちですが、このピンもコンフィグ前はハイインピーダンスとなりません。

このようなピンを上の図のような回路で、汎用I/OとしてJTAG自己書換えのアプリケーションに使用することはできません。

SpartanIIのデータシートによればFPGAのコンフィグに必要なメモリの容量は次のとおりです。

これによれば、XC2S150をコンフィグするためには1Mbitに収まります。XC2S150の場合は、汎用のシリアルEEPROMであるAT24C1024とマイコンを使った場合、ほとんどメモリに余裕はないのですが、XC2S100をコンフィグにAT24C1024を使った場合、FPGAのコンフィグデータに使われなかった267,360ビット(33,420バイトは)ユーザが自由に使うことができます。

表3 FPGAのコンフィグに必要なメモリ容量

|

デバイス |

サイズ(ビット) |

|---|---|

|

XC2S15 |

197,696 |

|

XC2S30 |

336,768 |

|

XC2S50 |

559,200 |

|

XC2S100 |

781,216 |

|

XC2S150 |

1,040,096 |

|

XC2S200 |

1,335,840 |

マイコンと汎用ROMを使ったコンフィグを行うと、余ったメモリをアプリケーション用データとして活用することもできます。しかしながら、純正のコンフィグROMを使った場合は、余ったメモリを活用することはできません。

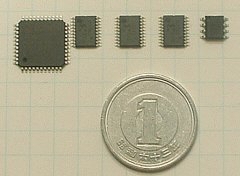

XILINXのツールで論理合成を行うと、bit streamファイルが生成されます。このbit streamファイルをFPGAのCCLKとDATAに対して流し込むことでコンフィグが可能です。

データの流し方は非常に簡単です。コンフィグ開始の前に、PROGにLのパルスを与え、その後CCLKの立ち上がりに同期してbit streamファイルをDATAから送り込むだけです。全てのデータを送り込むと、DONEのピンがLからHに遷移します。これによってFPGAが動作を開始したことがわかります。

図3 コンフィグ用データの波形

bit streamファイルの先頭には、設計の日時やデザイン名などの情報が記録されていますが、このデータも含めてFPGAに対して流し込んでも全く問題ありません。bit streamファイルにはFF FF FF FF AA 99 55 66で始まるレコードが記録されており、FPGAはFF FF FF FF AA 99 55 66で始まるデータ列をキーとして、コンフィグデータの開始を感知するためです。

なお、FPGAに流すデータはCRCでエラーチェックされます。エラーが発生した場合は、コンフィグ後にDONEピンがHにならないため、エラーであることがわかります。

昨今、手軽に使えるワンチップマイコンには、PIC、AVR、EZ-USB、H8などがあります。これらを使って、XILINXのFPGAをコンフィグすることを考えます。

選択肢はいくつかあります。まず、CPUの選定、ホストとPCとのインタフェースの選定、そしてメモリ種別の選定です。

2003年末現在では、次のようなインタフェースがPCと周辺機器の間で一般的に使用できます。

表4 PCで手軽に使えるインタフェース

|

種別 |

汎用性 |

速度 |

1Mbitをダウンロードするのに要するおおよその時間 |

|---|---|---|---|

|

RS-232C |

ほぼ必ず何らかの方法でインタフェース可能 |

115kbps |

11秒 |

|

パラレルポート(ECP) |

ノートPCでは不可な場合も多い。 |

12Mbps |

0.1秒 |

|

USB (FullSpeed) |

ほぼ必ず何らかの方法でインタフェース可能 |

12Mbps |

0.1秒 |

|

USB2.0 HighSpeed |

多くのPCで対応 |

480Mbps |

0.002秒 |

|

TCP/IP |

ほぼ必ず何らかの方法でインタフェース可能 |

10、100Mbps |

0.01秒 |

目標とするFPGAを、SpartanII用XC2S150とすると、のコンフィグROMは1Mbitですからダウンロード時間は上の表のようになります。

遅いと思われているRS-232Cでさえ、XC2S150をコンフィグするために1Mbitのデータを送るのに約11秒しか要しません。データを送るだけなら、JTAG経由でXC18をコンフィグする場合と大差ないか、それより早いでしょう。

むしろインタフェースの速度よりもROMの書き込みや消去にかかる時間の方が多くかかると思っていいでしょう。

2003年末現在で、容易に入手できる1Mbit以上のシリアルROMは、AT24C1024やSPIインタフェースのものがあります。秋葉原の店頭ではAT24C1024が購入でき、Digikeyなどの通販を利用すればATMELのAT45DB011などのSPIインタフェースのROMが500円前後で入手できます。

AT24C1024はインタフェースがI2Cのため速度は400kbpsまでですが、AT45DB011はSPIの20Mbpsまで可能です。

1Mbitのデータを読み出すため、AT24C1024は最短で2.5秒を要しますが、AT45DB011では0.05秒しか要しません。この速度は、FPGAをコンフィグする際に如何に速くROMのデータを読み出すことができるかということに影響します。すなわち、この時間は電源を投入してからFPGAが起動するまでの時間になります。

SPIの方が早くてよいのですが、AT24C1024は秋葉原の店頭で気軽に購入できるというメリットがあるうえ、ワンチップマイコンを使う場合、ほとんどの場合20Mbpsで読み出してFPGAにデータを送ることは不可能です。

FPGAの起動時間はそれほど気にしていないので、今回はAT24C1024で実験することにします。

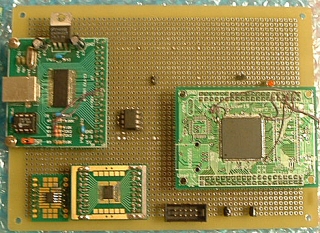

FPGAのコンフィグの実験を行うため、下の写真1のようなボードを製作しました。

写真1 コンフィグ実験用ボード

このボードは、次のような構成になっています。

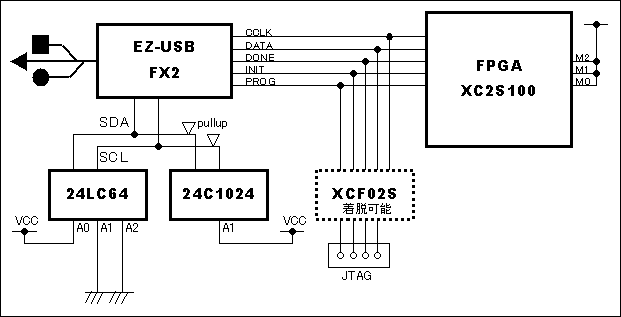

図4 製作した実験用ボードの回路

CPUにはモルフィー企画社製のEZ-USB FX2を使用しています。EZ-USB FX2にはプログラム用の24LC64と、FPGA用の24C1024が並列に接続されています。

CPUからはCCLK、DATA、DONE、INIT、PROGの5本の線がFPGAにつながっています。FPGAはスレーブシリアルモードで動作させるため、M2、M1、M0のピンをVCCに接続します。なお、マスターモードで動作させる場合は、M2、M1、M0をGNDに接続します。この切り替えはジャンパで行うことができます。

また、XCF01〜04も装着できるようになっています。

EZ-USB FX2の汎用I/Oは、56ピンパッケージではポートA、B、Dが使用可能です。このうちポートBは多くのアプリケーションではSlaveFIFOとして使われであろうと思われるので、FPGAのコンフィグには、ポートAかポートDを使用することにします。

ポートDもSlaveFIFOとして使用することができますが、56ピンパッケージではポートDをSlaveFIFOとしてしまうと、汎用I/Oの数が不足しますので、やむを得ずポートDも汎用I/Oにします。

その結果、ピンの割り当ては次のようになりました。もちろん、この割り当ては、ソフトウェアでどのようにも変更可能です。

表4 実験用ボードでのEZ-USBの端子割り当て

|

ポート |

ビット |

機能 |

|---|---|---|

|

A |

0 |

CCLK |

|

A |

1 |

DATA |

|

D |

0 |

DONE |

|

D |

1 |

INIT |

|

D |

2 |

PROG |

ソフトウェアは、EZ-USB上で動くファームウェアと、PC上で動く制御ソフトの両方を作成しました。

これらのソフトウェアはGPLライセンスで配布します。これらは一切無保証ですが、自由に改変して構いません。

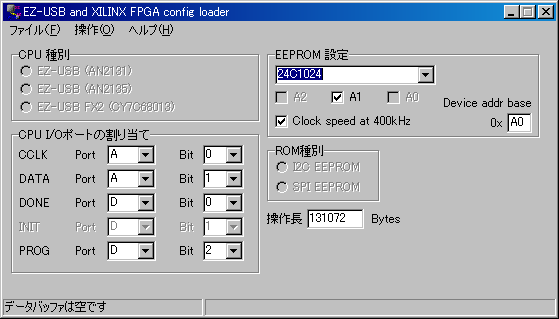

ソフトウェアの外観を、図?に示します。

使い方とダウンロードは「XILOADのページ」に記載してあります。

図5 作成したEZ-USB FX2操作用アプリケーション

XC2S100をコンフィグするために必要な時間を測定しました。

あるデザインのXC2S100のコンフィグ用bit streamファイルの長さは97722バイトであり、これは1MbitのROMの74%に相当します。

なお、EZ-USB FX2は48MHzで動作しています。

表5 コンフィグに要した時間

|

送信元 |

送信先 |

||

|---|---|---|---|

|

AT24C1024 |

ホストPC |

FPGA |

|

|

ホストPC(USB2.0) |

5.31秒※1 |

- |

2.23秒※3 |

|

AT24C1024 |

- |

2.83秒※2 |

2.55秒※4 |

|

XCF02S |

- |

- |

0.19秒※5 |

※1 USB経由でEEPROMへ書き込みを行う場合の時間に相当します。

※2 USB経由でEEPROMのデータを読み出す場合の時間に相当します。

※3 USB経由でFPGAへ直接データを書き込む場合の時間に相当します。

※4 シリアルEEPROMのデータをFPGAに書き込む場合の時間です。

※5 マスターモードで、通常のコンフィグROMを使う場合の時間です。

この実験では、XCFのような通常のROMを使用する場合、FPGAは電源投入後、約0.2秒で動作を開始できることになります。なお、マスターモードでXCFを使用した場合、FPGAが発するクロックは4MHz付近でした。

一方、ワンチップマイコンとして、EZ-USB FX2を利用した場合、電源投入後FPGAの動作開始まで、少なくとも2.55秒を要するようになります。

I2Cは、ACKと最初のアクセスのオーバーヘッドがあるため、効率を80%くらいと仮定しますと、I2Cのメモリから97722バイトを読み出すのに必要な時間は、97722バイト*8/(400kHz*80%)=約2.4秒となります。

I2Cからの読み出しはEZ-USBが持つハードウェアの機能で行い、FPGAへの書き込みは、I2Cからの読み出しと並列で行っていたのですが、SPIのROMを使った場合は読み出しをハードウェアでアクセラレートできませんので、コンフィグ時間は全体で5秒くらい必要になると思われます。

この遅さは、EZ-USB FX2のファームウェアをC言語で書いたことに起因するものです。もしアセンブラで書けば5倍くらい速くなると予測されます。

AT24C1024では0.5cm2という面積の目標はクリアできていないので、さらに次のことを試してみることにしましょう。

ご意見・ご要望は![]() nahitafu@nahitech.com

もしくは

nahitafu@nahitech.com

もしくは![]() 掲示板までお願いします。

掲示板までお願いします。