BSCANコンポーネントの使い方

平成16年12月14日

BSCANコンポーネントで何ができるのか?

BSCANコンポーネントで何ができるのか?

BSCANコンポーネントを使うと、FPGAとパソコンの間で通信ができます。

通信なら、USBやLAN、RS232C、パラレルポートがあるじゃないか、と思われるかもしれませんが、BSCANコンポーネントには次のようなメリットがあります。

- 追加部品が全くいらない

いかがでしょう?これは、ものすごいメリットです。

USBやLANは専用のチップが必要になりますし、RS232Cではレベル変換ICが必要です。パラレルポートだと10本くらいの配線をつなぎますしかさばります。部品がなくて秋葉原に買出しにいくことになるかもしれません。

でも、BSCANコンポーネントを使えば、FPGAやコンフィグROMの書き込みにも使われるJTAG信号線を利用して、追加部品を一切使わずに通信ができるのです。

ちなみに、BSCANという名前ですが本来のバウンダリスキャンではありません。

BSCANコンポーネントの原理

BSCANコンポーネントの原理

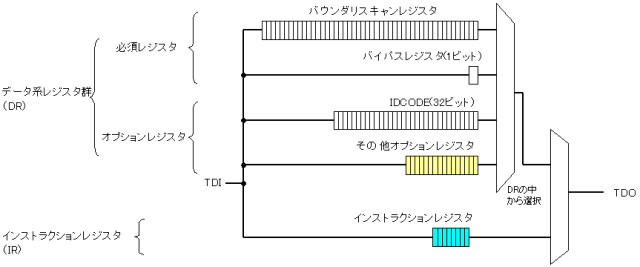

下の図は、一般的なJTAG対応デバイスの内部構造です。

図1 一般的なJTAG対応デバイスの内部構造

JTAGのTDIやTDOの信号は、デバイスの内部でシフト・レジスタにつながっています。そのシフト・レジスタは、TCKをクロックとして駆動されます。デバイスの内部には長さのことなるシフト・レジスタがいくつかあり、どのシフトレジスタを選択するかは、TMSやTDIで選択します。

上の図で、バウンダリ・スキャン・レジスタやバイパス・レジスタ、IDCODEレジスタは、ほとんどすべてのデバイスに用意されている標準的なものです。オプション・レジスタは、デバイスの書き込みや通信などそのデバイスの特徴を発揮するものです。

Spartan3の場合、インストラクション・レジスタの長さは6ビットです。このレジスタに、USER1(000010)あるいはUSER2(000011)というビットコードをセットすると、データ系に、ユーザが設計したシフト・レジスタを接続することができ、それがオプション・レジスタとなります。このオプションのシフト・レジスタは、ユーザが自ら設計しなければなりませんが、長さや使い方は自由です。また、JTAGの標準からは外れますが、シフト・レジスタではないものを接続することもできます。

なぜシフトレジスタなのか?

なぜシフトレジスタなのか?

JTAGはシリアル通信ですから、シリアル-パラレル変換を行うために使います。

使い方

使い方

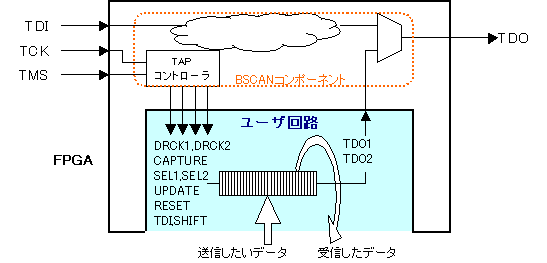

BSCANコンポーネントにはJTAGの信号線をデコードし、DRCK1やCAPTUREなどの信号をユーザ回路に出力します。

下の図2で青色の部分がユーザ回路、その上の凹型の部分がFPGA本体です。

図2

BSCANコンポーネントを使った場合のJTAGデバイスの構造

VHDLでの定義は次のようになっています。

リスト1 BSCANコンポーネントの定義

component BSCAN_SPARTAN3 |

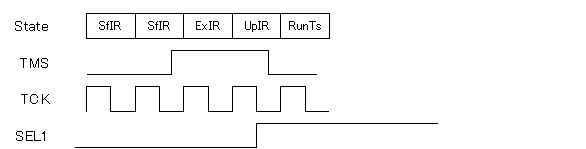

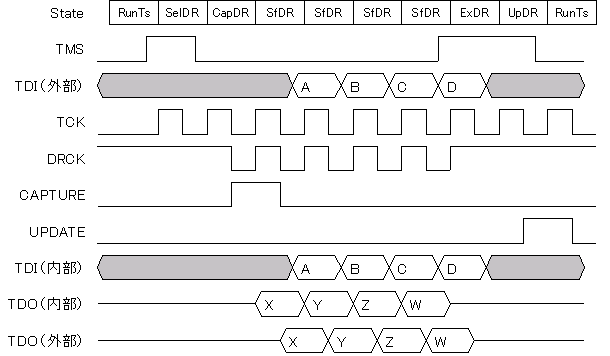

BSCANコンポーネントにはドキュメントがないようなので、タイミング等は独自に解析しました。その結果を次の図3、図4に載せます。

図3はUSER1命令を実行した場合のタイミングです。SEL1はUpdate-IRステートの、TCKの立下りタイミングでHに遷移します。逆に、BYPASS命令等を実行した場合、SELはTCKの立下りタイミングでLに戻ります。

図3

USER1命令をセットした場合のタイミング

図4はデータ系レジスタをシフトする際のタイミングです。CAPTURE等の信号はすべて、TCKの立下りタイミングで遷移します。Update-DRステートではDRCKは出力されませんので、ご注意ください。

図4

データレジスタシフト時のタイミング

実際に使用する場合は、いくつか注意すべき点があります。詳しくはお問い合わせください。

変則的な使い方

変則的な使い方

IEEE1149.1の標準からは外れますが、以下のような設計もあります。できるだけ使用しないほうが無難です。

UPDATEステートの扱い 影響度 ★☆☆

Update-DRの場合には、DRCKが出力されません。したがって、UPDATE信号をクロックとしてシフトレジスタからデータを取り出す必要があります。しかし、JTAGで送られてきた信号を使って、動作しているFPGAの内部に最終的にアクセスするためには、システムクロックに同期した信号にしなければなりません。

UPDATEでレジスタをコピーし、システムクロックに同期させてコピーすると、レジスタが2倍数必要になってしまいます。UPDATEを見ながらシステムクロックに同期させて取得すると、その辺を節約できますが、IEEE1149.1の標準からは外れます。

※システムクロックが入っていないとJTAGが使えないデバイスはこの理由が考えられる。

固定長ではないシフトレジスタ 影響度 ★★★

シフトレジスタの長さを可変にすることもできます。例えば、最初に入力された何ビットかを長さフィールドとして利用する場合や、データ中に特定のワードが現れた場合に最終部分と判断する方法などです。荒っぽい方法では、強制的にExit-DRステートに送るというのもあります。

![]()

図5

可変長のデータ

このような場合、CAPTUREステート以降のDRCKの数を数えることでうまくインタフェースが作れます。しかし、JTAGチェーンに別のデバイスが接続されると、全体のレジスタ長が変わってしまい、うまく動作しません。もちろん、IEEE1149.1の標準からは外れますが、TAPステートマシンを遷移させる必要がないので若干高速です。特定のボード限定など、ハードウェアが固定されている場合には有効でしょう。

※チェーン接続ができないと、データシートに明記されているデバイスはこの理由が考えられる。

シフトレジスタではないものがつながる 影響度 ★★★

JTAGでは、TDIから入ったデータは、何回かのシフトの後に必ずTDOから出てこなければなりません。ところが、フラッシュROMの書き換え完了フラグなど、1ビットのステータスだけが知りたい場合には、TDOにそのフラグを入れてしまう、という方法があります。もちろん、IEEE1149.1の標準からは外れますが、高速にフラグを参照することができます。

※チェーン接続ができないと、データシートに明記されているデバイスはこの理由が考えられる。

応用例

応用例

- 手軽な通信として(FPGAの回路にコマンドを与え、ステータスを読む)

- ブロックRAMの読み書き(FPGAにマイクロプロセッサを内蔵させ、そのメモリをJTAG経由で書き換える。マイコンのプログラム変更のたびにFPGAの設計をImprementし直さなくてよいのがメリット。)

- フラッシュROM書き換え(FPGA内にあらかじめ専用回路をつくっておき、BSCANコンポーネントで受信したデータを高速に読み書きする。バウンダリスキャンで読み書きするよりもずっと高速に操作できる。)

- TCP/IP over JTAG(FPGA内蔵マイコンとホストPCの間を仮想的なTCP/IPで通信。ハードウェアが不要なのがメリット。)

- JTAG over JTAG(さて、何に使おう)

![]()

お問い合わせは![]() nahitafu@nifty.comまでお願いします。

nahitafu@nifty.comまでお願いします。