|

TOPページへ戻る TOPページへ戻る |

ModelSIMの使い方 ModelSIMの使い方 |

| 1.はじめに |

| 2.ソースファイルの作成 |

| 3.シミュレーションファイルの作成 |

| 4.ModelSIMの起動 |

| 5.今後の課題 |

| メール |

御意見、御感想は 御意見、御感想はnahitafu at nifty com |

| Copyright |

| このWebページ上で紹介したすべての回路、情報、内容に関する著作権は私、なひたふが所有します。無断転載を固く禁じます。 (C)Copyright 1999-2001 Nahitafu |

|

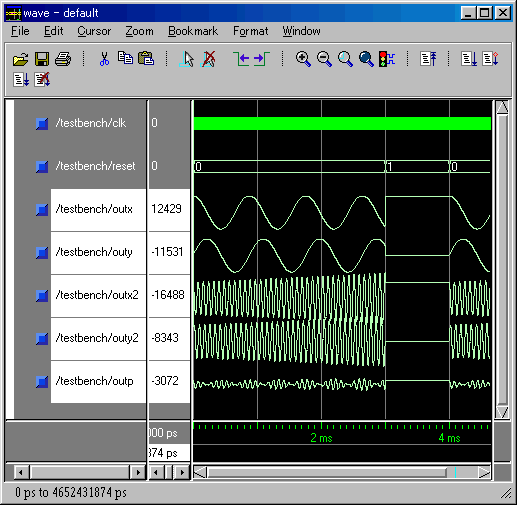

ModelSIM XILINX Edition Starterの使い方 1.はじめになぜXILINXとVHDLなのか?手論理圧縮から始まり、PALASMを経て、長い間ABELに親しんできた私ですが、今さらながらVHDLに傾いています。もちろんVHDLとABELを比較すれば、今でも私はABELの方が好きです。 昔はXILINXのツールといえばABELが標準で、VHDLとVeriligはオプション的な存在で、別料金でした。ところが、最近ではABELの方が亜流になってしまっています。WebPACKのVersion4以降では、ABELで書いたCPLDのソースも内部で一度VHDLに変換されてから処理されます。 そして何より、XILNIXのWebPACKではABELを使ってFPGAの設計ができません。何をやるにしても、FPGAでは多少のシミュレートが必要です。 独学で学んだVHDLなので、正しさは一切保証できかねますが、VHDLのシミュレーション方法を紹介します。 ModelSIM XILINX Edition Starter版とはModelSIMは、XILINX WebPackで使える強力なシミュレーションツールです。このツールを使うとCPLDやFPGAの出力波形をグラフィカルに観察することができるようになります。とても優れたツールです。 XILINXのWebPACKで無償で使えるModelSIMは、ModelSIMの中のXILINX Edition(XEという)の中の、さらにStarter版です。Starter版では500行までのソースのシミュレーションに限られていますが、回路を小分けにして、部分的にシミュレートしていけば、趣味の範囲では困ることはあまりないでしょう。そもそも500行のソースを書くことは結構大変です。 Starter版ではないXEでは10万ゲートまでシミュレーションできるそうですが、そんな大きなものを丸ごとシミュレーションする必要はあまりないでしょう。大きな回路ほど時間もかかりと思われます。 |