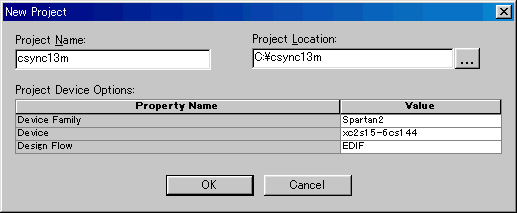

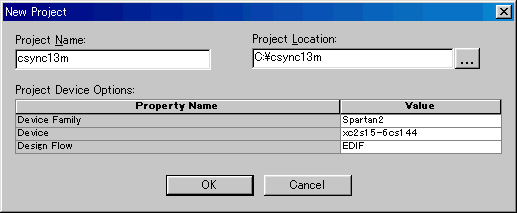

まず、WebPACKを起動したら、メインメニューから「File->New Project...」を選び、通常どおりにプロジェクトを作成します。

今回の例では、プロジェクト名は「csync13m」にしました。

上の図のダイアログが表示されたら、「Design Flow」の欄は「XST VHDL」にします。デフォルトでは「EDIF」になっていることがあるので、注意しましょう。もし間違えてEDIFでプロジェクトを作ってしまっても、後からプロパティーの変更をすればVHDLになるので焦らないでください。

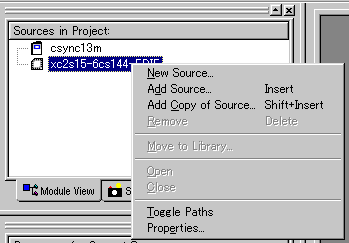

WebPACKでプロジェクトを作ったら、次に最初のソースファイルを作ります。デバイス名のところで右クリックをして、「New Source...」を選択します。

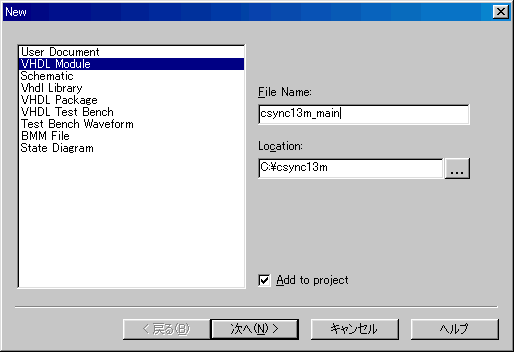

次に、作成するソースのタイプを選びます。「VHDL Module」を選択し、ファイル名を決めます。8文字を超えても大丈夫です。ここではcsync13m_mainとしました。

「次へ」ボタンを押したら次に開くダイアログで、ピン名を入力していくと自動的にVHDLの雛型を作ってくれます。VHDLのライブラリの宣言構文(IEEEなんたらかんたら・・・)や、ピンの宣言構文はなかなかフォーマットを覚えにくく、セミコロンの位置も微妙なので自分で作るのは面倒ですから、私はこの機能を重宝しています。

もし、新しくVHDLファイルを作るのではなく、過去に作ったVHDLファイルを利用する場合は、方法は2つあります。

次の章では実際にVHDLをシミュレーションしますが、その際に使用するVHDLファイルを下に載せます。これはビデオ信号処理回路で用いられる、NTSCインターレースな、コンポジット同期信号発生回路です。

--

-- CSYNC13 Version 1.1

--

-- Nahitafu's Free-IP

-- Sync generator for standard color NTSC signal Version 1.0

-- Clock frequency 13.500000MHz version

-- (C)Copyright 2000-2002 Nahitafu

--

-- see more detail --- http://member.nifty.ne.jp/nahitafu/

--

-- This can be fitted to XILINX XC9536PC44C , XC9536XLPC44C

--

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity csyncmain is

Port ( CLK : in std_logic; -- 13MHz

ENA : in std_logic;

RESET : in std_logic;

HPOS : inout std_logic_vector(9 downto 0);

VPOS : inout std_logic_vector(9 downto 0);

VSYNC : out std_logic;

HSYNC : out std_logic;

CSYNC : out std_logic;

FIELD : out std_logic;

HD : out std_logic;

VD : out std_logic;

VBLNK : inout std_logic;

BLANK : inout std_logic);

end csyncmain;

architecture Behavioral of csyncmain is

signal HBLNK : std_logic;

signal HSDOWN : std_logic;

signal HSUP : std_logic;

signal VSDOWN : std_logic;

signal VSUP : std_logic;

signal CSDOWN : std_logic;

signal CSUP : std_logic;

signal H20 : std_logic;

signal H52 : std_logic;

signal H84 : std_logic;

signal H385 : std_logic;

signal H449 : std_logic;

signal H481 : std_logic;

signal H814 : std_logic;

signal EQDUR : std_logic;

signal VSDUR : std_logic;

begin

process (CLK) begin

if(CLK'event and CLK = '1') then

if(RESET = '1') then

HPOS <= (others => '0');

VPOS <= "0000000001";

elsif(ENA = '1') then

if(HPOS = 857) then

HPOS <= (others => '0');

if(VPOS = 525) then VPOS <= "0000000001";

else VPOS <= VPOS + 1;

end if;

else

HPOS <= HPOS + 1;

end if;

end if;

end if;

end process; -- CLK

process(HPOS) begin

if(HPOS = 20) then H20 <= '1'; else H20 <= '0';end if;

if(HPOS = 52) then H52 <= '1'; else H52 <= '0';end if;

if(HPOS = 84) then H84 <= '1'; else H84 <= '0';end if;

if(HPOS = 385) then H385 <= '1'; else H385 <= '0';end if;

if(HPOS = 449) then H449 <= '1'; else H449 <= '0';end if;

if(HPOS = 481) then H481 <= '1'; else H481 <= '0';end if;

if(HPOS = 814) then H814 <= '1'; else H814 <= '0';end if;

end process; -- HPOS

process(H20,H84,H52,H385,H449,H481,H814,HPOS,VPOS,HBLNK,VBLNK,EQDUR,VSDUR) begin

-- condition of HSYNC up/down

if(H20 = '1') then HSDOWN <= '1';

else HSDOWN <= '0';

end if;

if(H84 = '1') then HSUP <= '1';

else HSUP <= '0';

end if;

-- condition of VSYNC up/down

if(((VPOS = 4) and H20 = '1') or ((VPOS = 266) and H449 = '1')) then VSDOWN <= '1';

else VSDOWN <= '0';

end if;

if(((VPOS = 7) and H20 = '1') or ((VPOS = 269) and H449 = '1')) then VSUP <= '1';

else VSUP <= '0';

end if;

--HBLK signal (Horizontal blanking duration , positive logic)

if((HPOS >= 0) and (HPOS <= 146)) then HBLNK <= '1';

else HBLNK <= '0';

end if;

--BLK signal (Blanking duration , negative logic)

if((HBLNK = '1') or (VBLNK = '1')) then BLANK <= '0';

else BLANK <= '1';

end if;

--condition of CSYNC down

if(H20 = '1' or (EQDUR = '1' and H449 = '1')) then CSDOWN <= '1';

else CSDOWN <= '0';

end if;

--condition of CSYNC up

if(H385 = '1' or H814 = '1' or (EQDUR = '0' and H84 = '1')

or (EQDUR = '1' and VSDUR = '0' and (H52 = '1' or H481 = '1'))) then CSUP <= '1';

else CSUP <= '0';

end if;

end process;

process(CLK) begin

if(CLK'event and CLK = '1') then

if(RESET = '1') then

HSYNC <= '1';

VSYNC <= '1';

CSYNC <= '1';

HD <= '0';

VD <= '0';

VBLNK <= '1';

FIELD <= '1';

EQDUR <= '1';

VSDUR <= '0';

else

--HSYNC trandition

if(HSUP = '1') then HSYNC <= '1';

elsif(HSDOWN = '1') then HSYNC <= '0';

end if;

--VSYNC trandition

if(VSUP = '1') then VSYNC <= '1';

elsif(VSDOWN = '1') then VSYNC <= '0';

end if;

--CSYNC trandition

if(CSUP = '1') then CSYNC <= '1';

elsif(CSDOWN = '1') then CSYNC <= '0';

end if;

--FIELD trandition

if((VPOS = 266) and H449 = '1') then FIELD <= '0';

elsif((VPOS = 4) and H20 = '1') then FIELD <= '1';

end if;

--VD signal (equal to inverting EQDUR signal)

if (((HPOS = 0) and (VPOS = 1)) or ((HPOS = 429) and (VPOS = 263))) then VD <= '0';

elsif(((HPOS = 0) and (VPOS = 10))or ((HPOS = 429) and (VPOS = 272))) then VD <= '1';

end if;

--HD signal

if (HPOS = 0) then HD <= '0';

elsif(HPOS = 84) then HD <= '1';

end if;

--VBLK signal (Vertical blanking duration , positive logic)

if (((HPOS = 0) and (VPOS = 0)) or((HPOS = 429) and (VPOS = 263))) then VBLNK <= '1';

elsif(((HPOS = 0) and (VPOS = 20))or((HPOS = 429) and (VPOS = 282))) then VBLNK <= '0';

end if;

--trandition of VS duration signal

if (((HPOS = 0) and (VPOS = 4)) or((HPOS = 429) and (VPOS = 266))) then VSDUR <= '1';

elsif(((HPOS = 0) and (VPOS = 7)) or((HPOS = 429) and (VPOS = 269))) then VSDUR <= '0';

end if;

--trandition of EQ duration signal

if(((HPOS = 0)and(VPOS = 1))or((HPOS = 429)and(VPOS = 263))) then EQDUR <= '1';

elsif(((HPOS = 0)and(VPOS = 10))or((HPOS = 429)and(VPOS = 272))) then EQDUR <= '0';

end if;

end if;

end if; -- clk

end process; -- clk

end Behavioral;

|